# 用户手册

APM32F107xBxC

APM32F105x8xBxC

基于 Arm® Cortex®-M3 内核的 32 位微控制器

版本: V 0.3(当前手册为 draft 版本,正式版本将于四月份发布)

# 目录

| 1   | 简介及文档描述规则     | 7  |

|-----|---------------|----|

| 1.1 | 简介            | 7  |

| 1.2 | 文档描述规则        | 7  |

| 2   | 系统架构          | 10 |

| 2.1 | 术语全称、缩写描述     | 10 |

| 2.2 | 系统架构框图        | 10 |

| 2.3 | 存储器映射         | 12 |

| 2.4 | 启动配置          | 12 |

| 3   | FLASH 存储器     | 14 |

| 3.1 | 术语全称、缩写描述     | 14 |

| 3.2 | 主要特征          | 14 |

| 3.3 | FLASH 存储器结构   | 14 |

| 3.4 | FLASH 存储器功能说明 | 15 |

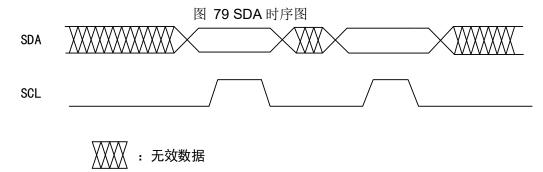

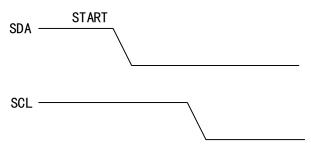

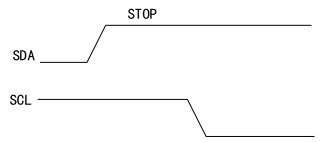

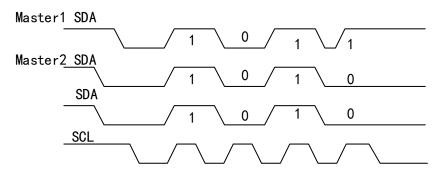

| 3.5 | 选项字节寄存器功能描述   | 17 |

| 3.6 | FMC 寄存器地址映射   | 18 |

| 3.7 | FMC 寄存器功能描述   | 19 |

| 4   | 复位与时钟管理(RCM)  | 23 |

| 4.1 | 术语全称、缩写描述     | 23 |

| 4.2 | 复位功能描述        | 23 |

| 4.3 | 时钟管理功能描述      | 25 |

| 4.4 | 寄存器地址映射       | 31 |

| 4.5 | 寄存器功能描述       | 31 |

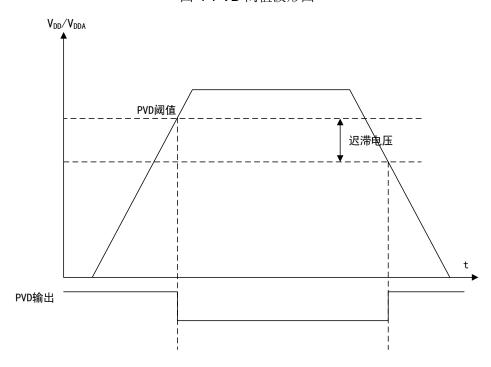

| 5   | 电源管理单元(PMU)   | 49 |

| 5.1 | 术语全称、缩写描述     | 49 |

| 5.2 | 简介            | 49 |

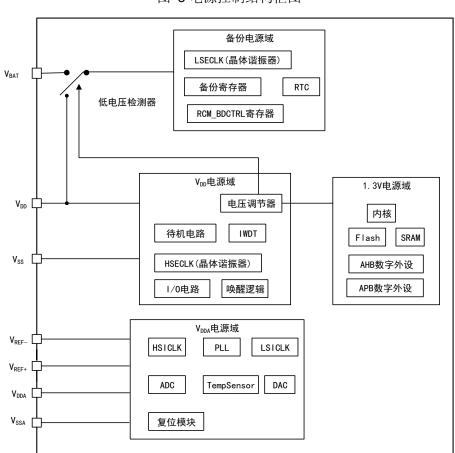

| 5.3 | 结构框图          | 49 |

| 5.4 | 功能描述          | 50 |

| 5.5 | 寄存器地址映射       | 54 |

| 5.6 | 寄存器功能描述       | 54 |

| 6   | 备份寄存器(BAKPR)  | 57 |

| 6.1 | 简介            | 57 |

| 6.2  | 主要特征             | 57 |

|------|------------------|----|

| 6.3  | 功能描述             | 57 |

| 6.4  | 寄存器地址映射          | 58 |

| 6.5  | 寄存器功能描述          | 58 |

| 7    | 嵌套向量中断控制器(NVIC)  | 61 |

| 7.1  | 术语全称、缩写描述        | 61 |

| 7.2  | 简介               | 61 |

| 7.3  | 主要特征             | 61 |

| 7.4  | 中断和异常向量表         | 61 |

| 8    | 外部中断/事件控制器(EINT) | 65 |

| 8.1  | 简介               | 65 |

| 8.2  | 主要特征             | 65 |

| 8.3  | 功能描述             | 65 |

| 8.4  | 寄存器地址映射          | 67 |

| 8.5  | 寄存器功能描述          | 68 |

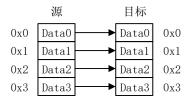

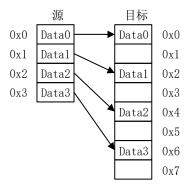

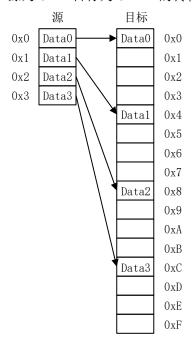

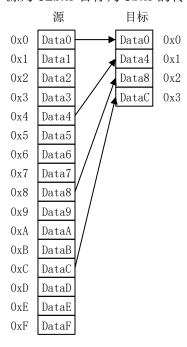

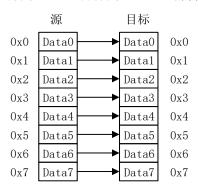

| 9    | 直接存储器存取(DMA)     | 70 |

| 9.1  | 术语全称、缩写描述        | 70 |

| 9.2  | 简介               | 70 |

| 9.3  | 主要特征             | 70 |

| 9.4  | 功能描述             | 71 |

| 9.5  | 寄存器地址映射          | 76 |

| 9.6  | 寄存器功能描述          | 77 |

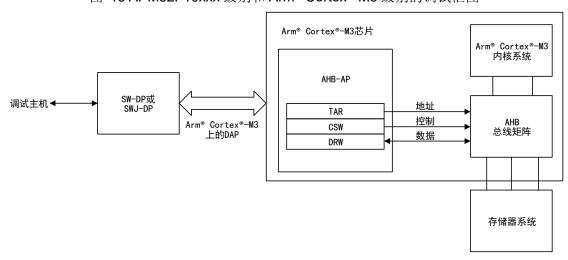

| 10   | 调试 MCU(DBGMCU)   | 81 |

| 10.1 | 术语全称、缩写描述        | 81 |

| 10.2 | 简介               | 81 |

| 10.3 | 主要特征             | 81 |

| 10.4 | 功能描述             | 82 |

| 10.5 | 寄存器地址映射          | 83 |

| 10.6 | 寄存器功能描述          | 83 |

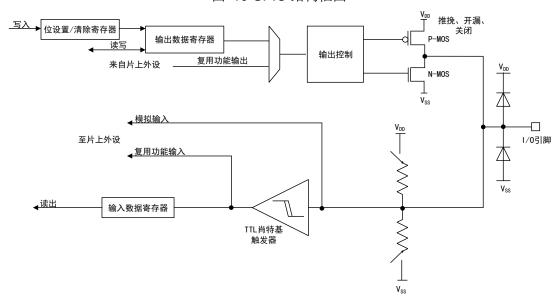

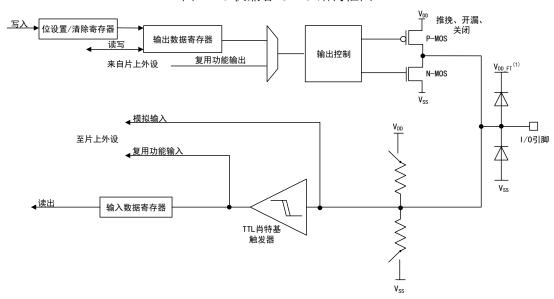

| 11   | 通用输入/输出引脚(GPIO)  | 86 |

| 11.1 | 术语全称、缩写描述        | 86 |

| 11.2 | 主要特征             | 86 |

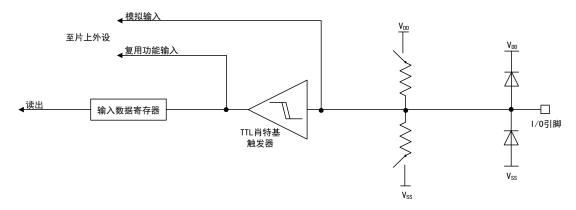

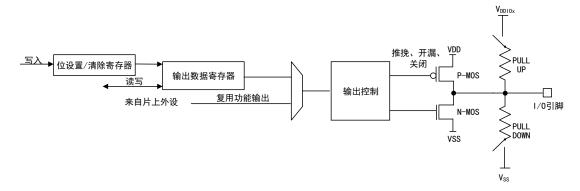

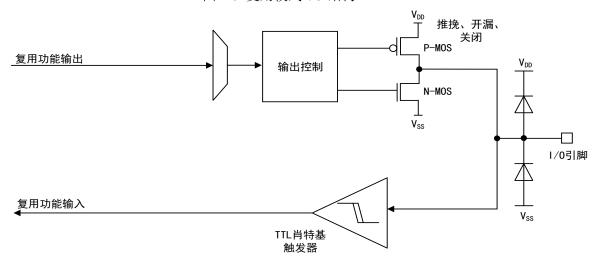

| 11.3 | 结构框图             | 87 |

| 11.4 | 功能描述              | 87  |

|------|-------------------|-----|

| 11.5 | 寄存器地址映射           | 90  |

| 11.6 | 寄存器功能描述           | 91  |

| 12   | 复用功能输入输出引脚(AFIO)  | 94  |

| 12.1 | 简介                | 94  |

| 12.2 | 功能描述              | 94  |

| 12.3 | 寄存器地址映射           | 98  |

| 12.4 | 寄存器功能描述           | 98  |

| 13   | 定时器概述             | 104 |

| 13.1 | 术语全称、缩写描述         | 104 |

| 13.2 | 定时器类别及主要差异        | 104 |

| 14   | 高级定时器(TMR1)       | 107 |

| 14.1 | 简介                | 107 |

| 14.2 | 主要特征              | 107 |

| 14.3 | 结构框图              | 108 |

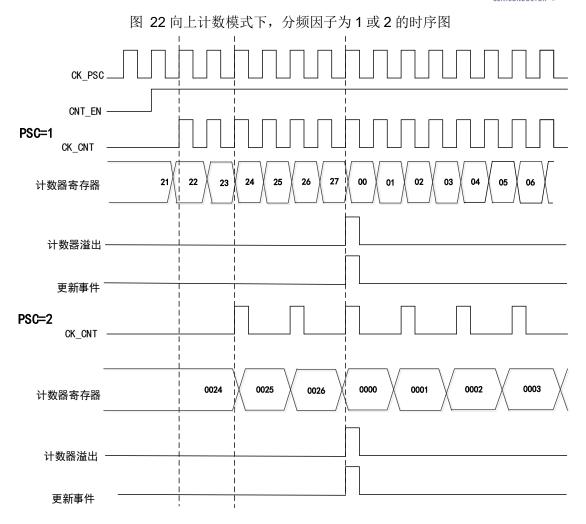

| 14.4 | 功能描述              | 108 |

| 14.5 | 寄存器地址映射           | 124 |

| 14.6 | 寄存器功能描述           | 125 |

| 15   | 通用定时器(TMR2/3/4/5) | 143 |

| 15.1 | 简介                | 143 |

| 15.2 | 主要特征              | 143 |

| 15.3 | 结构框图              | 144 |

| 15.4 | 功能描述              | 144 |

| 15.5 | 寄存器地址映射           | 156 |

| 15.6 | 寄存器功能描述           | 157 |

| 16   | 基本定时器(TMR6/7)     | 172 |

| 16.1 | 简介                | 172 |

| 16.2 | 主要特征              | 172 |

| 16.3 | 结构框图              | 172 |

| 16.4 | 功能描述              | 172 |

| 16.5 | 寄存器地址映射           | 174 |

| 16.6 | 寄存器功能描述           | 174 |

| 17   | 看门狗定时器(WDT)       | 178 |

| 17.1 | 简介                              | 178 |

|------|---------------------------------|-----|

| 17.2 | 独立看门狗定时器(IWDT)                  | 178 |

| 17.3 | 窗口看门狗定时器(WWDT)                  | 179 |

| 17.4 | IWDT 寄存器地址映射                    | 181 |

| 17.5 | IWDT 寄存器功能描述                    | 181 |

| 17.6 | WWDT 寄存器地址映射                    | 182 |

| 17.7 | WWDT 寄存器功能描述                    | 183 |

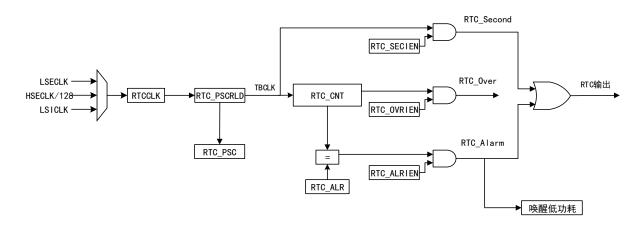

| 18   | 实时时钟(RTC)                       | 185 |

| 18.1 | 术语全称、缩写描述                       | 185 |

| 18.2 | 主要特征                            | 185 |

| 18.3 | 结构框图                            | 185 |

| 18.4 | 功能描述                            | 186 |

| 18.5 | 寄存器地址映射                         | 187 |

| 18.6 | 寄存器功能描述                         | 187 |

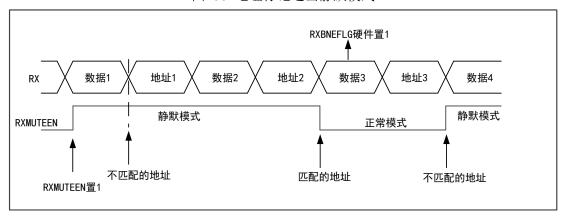

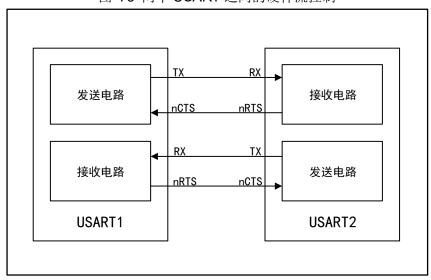

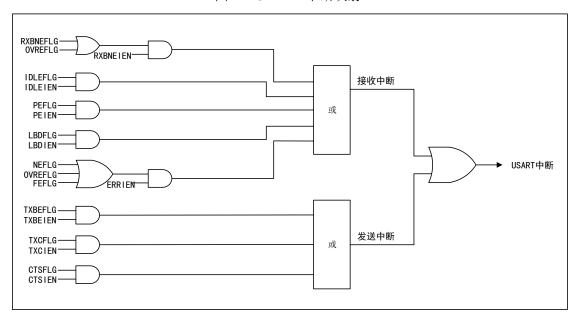

| 19   | 通用同步异步收发器(USART)                | 191 |

| 19.1 | 术语全称、缩写描述                       | 191 |

| 19.2 | 简介                              | 191 |

| 19.3 | 主要特征                            | 191 |

| 19.4 | 功能描述                            | 192 |

| 19.5 | 寄存器地址映射                         | 204 |

| 19.6 | 寄存器功能描述                         | 205 |

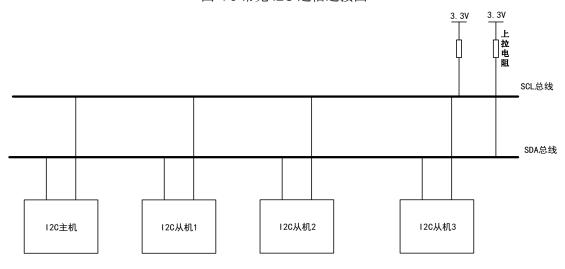

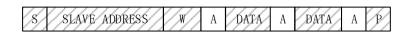

| 20   | 内部集成电路接口( <b>I2C</b> )          | 212 |

| 20.1 | 术语全称、缩写描述                       | 212 |

| 20.2 | 简介                              | 212 |

| 20.3 | 主要特征                            | 212 |

| 20.4 | 结构框图                            | 213 |

| 20.5 | 功能描述                            | 214 |

| 20.6 | 寄存器地址映射                         | 220 |

| 20.7 | 寄存器功能描述                         | 220 |

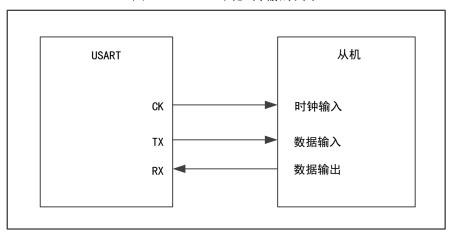

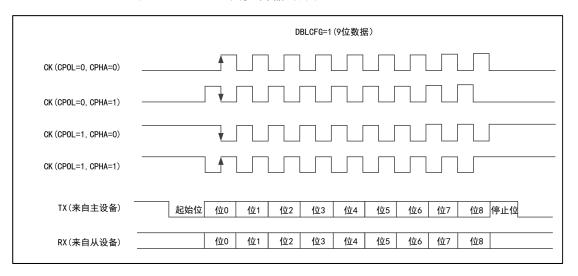

| 21   | 串行外设接口/片上音频接口( <b>SPI/I2S</b> ) | 229 |

| 21.1 | 术语全称、缩写描述                       | 229 |

| 21.2 | 简介                              | 229 |

| 21.3 | 主要特征                            | 229 |

| 21.4  | SPI 功能描述                            | 230 |

|-------|-------------------------------------|-----|

| 21.5  | I2S 功能描述                            | 240 |

| 21.6  | 寄存器地址映射                             | 250 |

| 21.7  | 寄存器功能描述                             | 250 |

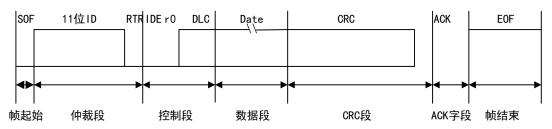

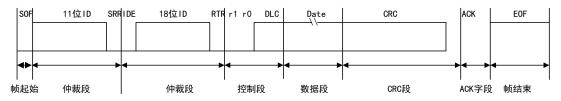

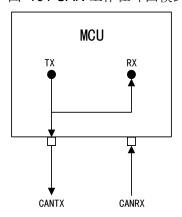

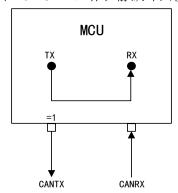

| 22    | 控制器局域网(CAN)                         | 257 |

| 22.1  | 术语全称、缩写描述                           | 257 |

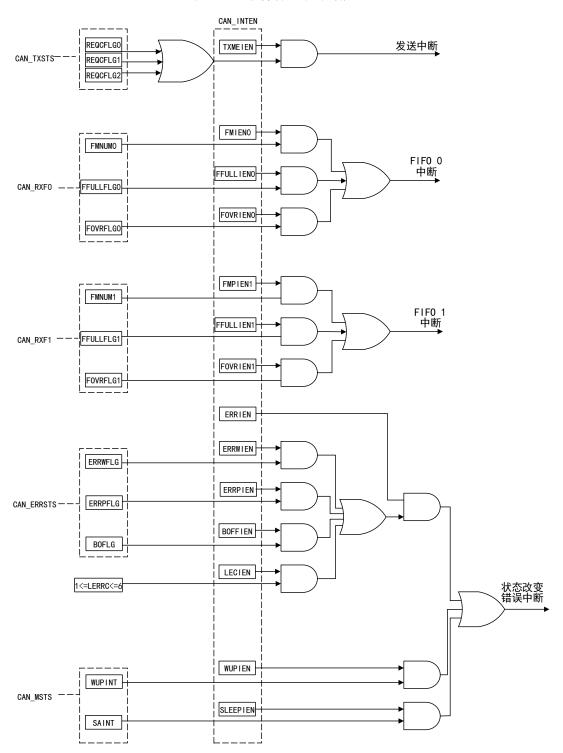

| 22.2  | 简介                                  | 257 |

| 22.3  | 主要特征                                | 257 |

| 22.4  | 功能描述                                | 257 |

| 22.5  | 寄存器地址映射                             | 265 |

| 22.6  | 寄存器功能描述                             | 266 |

| 23    | USB OTG_FS                          | 280 |

| 23.1  | 简介                                  | 280 |

| 23.2  | OTG_FS 全局寄存器地址映射                    | 280 |

| 23.3  | OTG_FS 全局寄存器功能描述                    | 281 |

| 23.4  | OTG_FS 主机模式寄存器地址映射                  | 294 |

| 23.5  | OTG_FS 主机模式寄存器功能描述                  | 294 |

| 23.6  | OTG_FS 设备模式寄存器地址映射                  | 301 |

| 23.7  | OTG_FS 设备模式寄存器功能描述                  | 302 |

| 23.8  | 全速 OTG 电源和时钟门控控制寄存器(OTG_FS_PCGCTRL) | 314 |

| 24    | 以太网(ETHERNET)                       | 315 |

| 24.1  | 简介                                  | 315 |

| 24.2  | 以太网主要特征                             | 315 |

| 24.3  | 功能描述                                | 317 |

| 24.4  | MAC 寄存器地址映射                         | 339 |

| 24.5  | MAC 寄存器功能描述                         | 339 |

| 24.6  | MMC 寄存器地址映射                         | 351 |

| 24.7  | MMC 寄存器功能描述                         | 351 |

| 24.8  | PTP 寄存器地址映射                         | 354 |

| 24.9  | PTP 寄存器功能描述                         | 355 |

| 24.10 | DMA 寄存器地址映射                         | 357 |

| 24.11 | DMA 寄存器功能描述                         | 358 |

| 25    | 模数转换器(ADC)                          | 367 |

| 25.1 | 术语全称、缩写描述       | 367 |

|------|-----------------|-----|

| 25.2 | 简介              | 368 |

| 25.3 | 主要特征            | 368 |

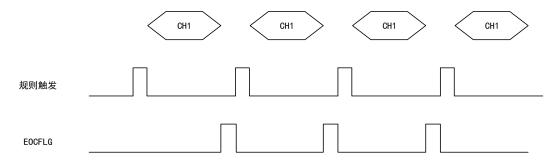

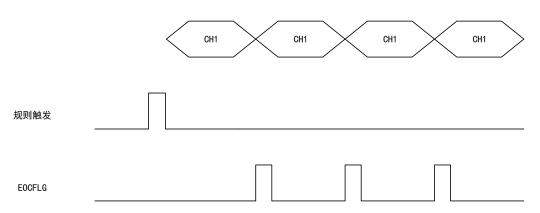

| 25.4 | 功能描述            | 369 |

| 25.5 | 寄存器地址映射         | 378 |

| 25.6 | 寄存器功能描述         | 378 |

| 26   | 数模转换器(DAC)      | 387 |

| 26.1 | 术语全称、缩写描述       | 387 |

| 26.2 | 简介              | 387 |

| 26.3 | 结构框图            | 387 |

| 26.4 | 功能描述            | 387 |

| 26.5 | 寄存器地址映射         | 390 |

| 26.6 | 寄存器功能描述         | 391 |

| 27   | 循环冗余校验计算单元(CRC) | 396 |

| 27.1 | 简介              | 396 |

| 27.2 | 功能描述            | 396 |

| 27.3 | 寄存器地址映射         | 396 |

| 27.4 | 寄存器功能描述         | 396 |

| 28   | 芯片电子签名          | 398 |

| 28.1 | 主存储区容量寄存器       | 398 |

| 28.2 | 96 位唯一芯片 ID     | 398 |

| 29   | 版本历史            | 400 |

# 1 简介及文档描述规则

# 1.1 简介

本用户手册向应用程序开发人员提供关于如何使用 MCU (微控制器) 系统架构、存储器和外设所涉及的全部信息。

关于 Arm® Cortex®-M3 内核的相关信息,请参考 Arm® Cortex®-M3 技术参考手册;关于型号信息、尺寸和器件的电气特性等详细数据请参考对应的数据手册(datasheet);有关 MCU 系列全部型号中,存储器映射、外设存在情况及其数目请查阅相应的数据手册。

在此说明:珠海极海半导体有限公司,在以下正文中,简称"Geehy"。

# 1.2 文档描述规则

### 1.2.1 "寄存器功能描述"规则

- (1) 控制类(CTRL)寄存器,未特别说明,都是"软件置 1 和清 0"。

- (2) 控制类寄存器后面一般会有动词缩写以作区别,动词可以有: EN-Enable、CFG-Configure、D-Disable、SET-Setup、SEL-Select

- (3) 状态类寄存器缩写后面一般会有 FLG 以作区别。

- (4) 数值、数据类寄存器,一般会包括 V、VALUE、D、DATA,这些词后面不加动词,比如:xxPSC,CNT,后面一般不添加动词。

### 1.2.2 术语全称、缩写描述

表格 1 RW 方式缩写及描述

| R/W 方式                  | 描述                                | 缩写    |

|-------------------------|-----------------------------------|-------|

| read/write              | 软件能读写此位。                          | R/W   |

| read-only               | 软件只能读此位。                          | R     |

| write-only              | 软件只能写此位,读此位将返回复位值。                | W     |

| read/clear              | 软件可以读此位,也可以通过写 1 清除此位,写 0 对此位无影响。 | RC_W1 |

| read/clear              | 软件可以读此位,也可以通过写0清除此位,写1对此位无影响。     | RC_W0 |

| read/clear by read      | 软件可以读此位,读此位将自动地清除它为0,写该位无效。       | RC_R  |

| read/set                | 软件可以读也可以设置此位,写0对此位无影响。            | R/S   |

| read-only write trigger | 软件可以读此位,写0或1触发一个事件但对此位数值没有影响。     | RT_W  |

| toggle                  | 软件只能通过写 1 来翻转此位,写 0 对此位无影响。       | Т     |

表格 2 常用寄存器功能描述术语全称、缩写

| 中文全称 | 英文全称   | 英文缩写 |

|------|--------|------|

| 使能   | Enable | EN   |

| 中文全称 | 英文全称        | 英文缩写 |

|------|-------------|------|

| 禁止   | Disable     | D    |

| 清除   | Clear       | CLR  |

| 选择   | Select      | SEL  |

| 配置   | Configure   | CFG  |

| 控制   | Contrl      | CTRL |

| 控制器  | Controller  | С    |

| 复位   | Reset       | RST  |

| 停止   | Stop        | STOP |

| 设置   | Set         | SET  |

| 装载   | Load        | LD   |

| 校准   | Calibration | CAL  |

| 初始化  | Initialize  | INIT |

| 错误   | Error       | ERR  |

| 状态   | Status      | STS  |

| 准备   | Ready       | RDY  |

| 软件   | Software    | SW   |

| 硬件   | Hardware    | HW   |

| 源    | Source      | SRC  |

| 系统   | System      | SYS  |

| 外设   | Peripheral  | PER  |

| 地址   | Address     | ADDR |

| 方向   | Direction   | DIR  |

| 时钟   | Clock       | CLK  |

| 输入   | Input       | I    |

| 输出   | Output      | 0    |

| 中断   | Interrupt   | INT  |

| 数据   | Data        | DATA |

| 大小   | Size        | SIZE |

| 除法器  | Divider     | DIV  |

| 预分频器 | Prescaler   | PSC  |

| 乘法器  | Multiplier  | MUL  |

| 周期   | Period      | PRD  |

表格 3 模块全称、简写

| 中文全称        | 英文全称                                                     | 英文缩写    |

|-------------|----------------------------------------------------------|---------|

| 外部存储控制器     | External Memory Controller                               | EMMC    |

| 静态存储控制器     | Static Memory Controller                                 | SMC     |

| 动态存储控制器     | Dynamic memory Controller                                | DMC     |

| 复位与时钟管理单元   | Reset and Clock Management Unit                          | RCM     |

| 电源管理单元      | Power Management Unit                                    | PMU     |

| 备份寄存器       | Backup Register                                          | BAKPR   |

| 嵌套向量中断控制器   | Nested Vector Interrupt Controller                       | NVIC    |

| 外部中断/事件控制器  | External Interrupt /Event Controller                     | EINT    |

| 直接存储器存取     | Direct Memory Access                                     | DMA     |

| 调试 MCU      | Debug MCU                                                | DBG MCU |

| 通用输入/输出引脚   | General-Purpose Input Output Pin                         | GPIO    |

| 复用功能输入/输出引脚 | Alternate Function Input Output Pin                      | AFIO    |

| 定时器         | Timer                                                    | TMR     |

| 看门狗定时器      | Watchdog Timer                                           | WDT     |

| 独立看门狗       | Independent Watchdog Timer                               | IWDT    |

| 窗口看门狗       | Windows Watchdog Timer                                   | WWDT    |

| 实时时钟        | Real-Time Clock                                          | RTC     |

| 通用同步异步收发器   | Universal Synchronous Asynchronous  Receiver Transmitter | USART   |

| 内部集成电路接口    | Inter-Integrated Circuit Interface                       | I2C     |

| 串行外设接口      | Serial Peripheral Interface                              | SPI     |

| 片上音频接口      | Inter-IC Sound Interface                                 | 128     |

| 四线串行外围接口    | Quad Serial Peripheral Interface                         | QSPI    |

| 控制器局域网      | Controller Area Network                                  | CAN     |

| 安全数字输入输出    | Secure Digital Input and Output                          | SDIO    |

| 全速 USBD 接口  | Universal Serial Bus Full-Speed Device                   | USBD    |

| 模拟数字转换器     | Analog-to-Digital Converter                              | ADC     |

| 数字模拟转换器     | Digital-to-Analog Converter                              | DAC     |

| 循环冗余校验计算单元  | Cyclic Redundancy Check Calculation Unit                 | CRC     |

| 浮点运算单元      | Float Point Unit                                         | FPU     |

|             | 1                                                        | j.      |

# 2 系统架构

# 2.1 术语全称、缩写描述

表格 4 术语全称、缩写描述

| 中文全称    | 英文全称                          | 英文缩写 |

|---------|-------------------------------|------|

| 高级高性能总线 | Advanced High-Performance Bus | AHB  |

| 高级外围总线  | Advanced Peripheral Bus       | APB  |

| 设备固件升级  | Device Firmware Update        | DFU  |

# 2.2 系统架构框图

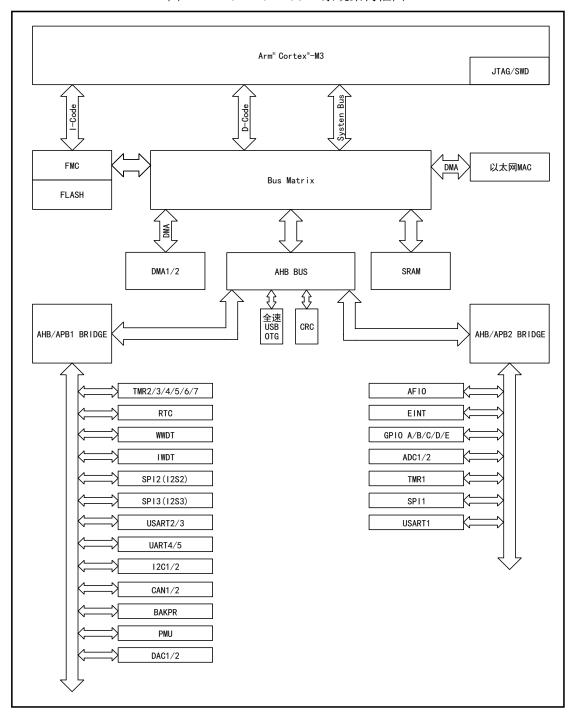

主系统主要由五个驱动单元和三个被动单元构成。五个驱动单元分别是连接 Arm® Cortex®-M3 内核的 DCode 总线(D-bus)、系统总线(S-bus)、通用 DMA1、DMA2 和以太网 DMA。三个被动单元分别是内部 SRAM、内部闪存存储器和 AHB 到 APB 的桥(AHB/APBx),其中,AHB/APBx 连接所有的 APB 设备。

这些都是通过一个多级的 AHB 总线构架相互连接的,如下图所示:

### 图 1 APM32F107 105xx 系统架构框图

### 注意:

- (1) F107 型号产品仅有 1 个 I2C; F105 型号产品有 2 个 I2C。

- (2) F107 型号产品有以太网单元; F105 型号产品没有以太网单元。

表格 5 总线名称

| 名称        | 说明                                        |

|-----------|-------------------------------------------|

| ICode Bus | 连接 Arm® Cortex®-M3 内核的指令总线与闪存指令接口。用于预取指令。 |

| 名称        | 说明                                                                                        |

|-----------|-------------------------------------------------------------------------------------------|

| DCode Bus | 连接 Arm® Cortex®-M3 内核的 DCode 总线与闪存存储器的数据接口。用于加载常量和访问调试。                                   |

| 系统总线      | 连接 Arm® Cortex®-M3 内核的系统总线(外设总线)与总线矩阵。                                                    |

| DMA 总线    | 连接 DMA 的 AHB 主控接口与总线矩阵。                                                                   |

| 总线矩阵      | 协调内核和 DMA 的访问,协调 CPU 的 DCode 和 DMA 到 SRAM、Flash 和外设的访问。AHB 外设通过总线矩阵与系统总线相连,允许 DMA 访问。     |

| AHB/APB 桥 | 两个桥在 AHB 和两个 APB 总线间提供同步连接。APB1, APB2 的最高操作速度不同。<br>当对 APB 寄存器进行非 32 位访问时,访问会被自动转换成 32 位。 |

# 2.3 存储器映射

存储器映射地址总共是 4GB 地址,分配的地址包括内核(包括内核外设)、片上 Flash(包括主存储区、系统存储区、选项字节)、片上 SRAM、EMMC、总线外设(包括 AHB、APB 外设),各类地址具体信息请参考对应型号的数据手册。

## 2.3.1 嵌入式 SRAM

内置静态 SRAM。它可以以字节、半字(16 位)或全字(32 位)访问。SRAM 的起始地址是 0x2000 0000。

### 2.3.2 位段

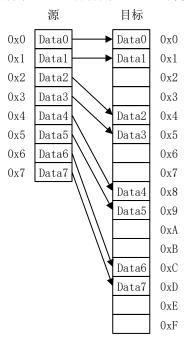

Arm® Cortex®-M3 存储器映射有两个位段(bit-band)区,它将每个在别名存储器区中的字映射到位段存储器的一个位。在别名存储区写入一个字,会有对位段区的目标执行读-改-写操作的相同效果。外设寄存器和 SRAM 都被映射到一个位段区里,允许执行单一的位段的写和读操作。

下面给出一份映射公式:

bit\_word\_addr=bit\_band\_base+ (byte\_offset×32) + (bit\_number×4)

详细信息请参考《Arm® Cortex®-M3 技术参考手册》

# 2.4 启动配置

由于 Arm® Cortex®-M3 内核的 CPU 从 ICode Bus(指令总线)获取复位向量,导致启动只能从代码区开始,典型为 Flash 存储器启动。但是,APM32F 微控制器系列实现了一个特殊的机制,通过配置 BOOT[1:0]引脚参数,可以用有三种不同的启动模式,即系统可以不仅仅从 Flash 存储器或系统存储器启动,还可以从内置 SRAM 启动。被选作启动区域的存储器是由选择的启动模式决定的。

表格 6 启动模式配置及其访问方式

| 启动模式选择引脚 |       | 启动模式                                         | ete karte et                                                 |

|----------|-------|----------------------------------------------|--------------------------------------------------------------|

| BOOT1    | воото | <b>一                                    </b> | 访问方式                                                         |

| Х        | 0     | 主闪存存储器<br>(Flash)                            | 主闪存存储器被映射到启动空间,但仍然能够<br>在它原有的地址访问它,即闪存存储器的内容<br>可以在两个地址区域访问。 |

| 0        | 1     | 系统存储器                                        | 系统存储器被映射到启动空间(0x0000<br>0000),但仍然能够在它原有的地址访问它。               |

| 1        | 1     | 内置 SRAM                                      | 只能在开始的地址区访问 SRAM。                                            |

#### 注意:

- (1) 启动空间地址为 0x0000 0000

- (2) Flash 原有地址为 0x0800 0000

- (3) 系统存储器原有地址为 0x1FFF B000

- (4) SRAM 的起始地址为 0x2000 0000

用户可以通过设置 BOOT1 和 BOOT0 引脚的状态,来选择在复位后的启动模式。

BOOT 引脚应在待机模式下保持用户需要的启动配置,当从待机模式退出时,引脚的值会被锁存。如果选择从内置 SRAM 启动,那么在编写应用代码时,必须使用 NVIC 的异常表和偏移寄存器,重新将向量表映射至 SRAM 中。

### 内嵌的启动程序

内嵌的启动程序由 Geehy 在生产线上写入并存放在系统存储区域,通过 USRAT1、USART2(重映像)、CAN2(重映像)或 USB OTG\_FS 的设备模式 (DFU) 启用启动程序,可以对 Flash 存储器进行重新编程。出厂后,此区域会被锁定以防用户擦写。

注意:由于使用 USB OTG\_FS 设备模式需要配备上拉电阻,所以用户可以通过将高电平接入 PA9 引脚来激活内部上拉电阻,或者外接一个上拉电阻。

# 3 Flash 存储器

本章主要介绍 Flash 的存储结构、读、擦、写、读/写保护、解锁/锁定特性,及涉及到的寄存器功能描述。

# 3.1 术语全称、缩写描述

表格 7 术语全称、缩写描述

| 中文全称     | 英文全称                    | 英文缩写 |

|----------|-------------------------|------|

| 闪存存储器控制器 | Flash Memory Controller | FMC  |

# 3.2 主要特征

- (1) Flash 存储器结构

- 分为主存储区、信息块

- 主存储区容量最高为 256KB

- 信息块分为系统存储区、选项字节

- 系统存储区容量大小为 18KB,存放 BootLoader 程序、96 位唯一 UID、主存储区容量信息

- 选项字节区容量大小为 16Bytes

- (2) 功能说明

- 读取 Flash

- 页/片擦 Flash

- 写 Flash

- 读/写保护 Flash

- 配置选项字节

# 3.3 Flash 存储器结构

表格 8 APM32F107 105xx 系列产品 Flash 存储结构

| 块    | 名称    | 地址范围                      | 大小 (字节) |

|------|-------|---------------------------|---------|

| 主存储块 | 页 0   | 0x0800 0000 - 0x0800 07FF | 2K      |

| 主存储块 | 页 1   | 0x0800 0800 - 0x0800 0FFF | 2K      |

| 主存储块 | 页 2   | 0x0800 1000 - 0x0800 17FF | 2K      |

| 主存储块 | 页 3   | 0x0800 1800 - 0x0800 1FFF | 2K      |

| 主存储块 |       |                           | •••     |

| 主存储块 | 页 127 | 0x0803 F800 - 0x0803 FFFF | 2K      |

| 信息块  | 系统存储区 | 0x1FFF B000 - 0x1FFF F7FF | 18K     |

| 信息块  | 选项字节  | 0x1FFF F800 - 0x1FFF F80F | 16      |

注: APM32F107 105xx 系列产品的主存储块包含页的数量和具体产品的 Flash 容量有关。

# 3.4 Flash 存储器功能说明

描述对主存储器、信息块(包括系统存储区、选项字节)的操作,包括读、写、擦、读/写保护。

读取 Flash 包括主存储块、信息块,擦、写、读/写保护分开介绍;系统存储区在出厂时已写入,用户无法修改,不介绍该模块的擦、写、读/写保护。

## 3.4.1 读取 Flash

Flash 存储器可直接寻址,读取 Flash 受以下配置影响:

#### 等待周期

针对不同的系统时钟需配置不同的等待周期:

- 0个等待周期: 0<系统时钟≤24MHz

- 1 个等待周期: 24MHz<系统时钟≤48MHz

- 2 个等待周期: 48MHz<系统时钟≤72MHz

- 3 个等待周期: 72MHz<系统时钟≤96MHz

### 预取缓存区

可提高读取速度,每次复位预取缓存区被自动打开;带预取缓存的读接口,APM32F107 105xx 系列是 2×128 位;只有系统时钟和 AHB 时钟一致且系统时钟小于 24MHz 时才能配置开启或关闭。

#### 半周期访问

在需要优化功耗时可使用半周期访问,此时系统时钟和 AHB 时钟一致,且系统时钟为 8MHz 或低于 8MHz 才能使用半周期访问 Flash,否则必须处于开启状态。

### 3.4.2 主存储块

#### 3.4.2.1 擦主存储块

FMC 支持页擦除和整片擦除(全擦除)两种方式将主存储区的内容初始化为高电平(数据表现为 0xFFFF)。用户在对 Flash 进行写入前,建议对写入地址页先进行擦除操作,若写入地址的数据不是 0xFFFF 则会触发一个编程错误。

#### 主存储器页擦除

页擦除是根据程序选择的主存储区页进行独立擦除,不会对未选择擦除的页产生 任何影响。

正确的页擦除(或闪存写入操作)结束后,FMC\_STS 寄存器的 OCF 将会被置位,若开启了 OCIE 中断则将触发一个操作完成中断。用户需要注意的是选择擦除的页必须是有效的页(主存储区有效的地址和未被写保护的地址)。

#### 主存储器片擦除

片擦除操作将会使 Flash 主存储区内所有内容全部被擦除,片擦除会使主存储区 所有数据全部擦除,用户在使用时需要特别注意,以避免误操作导致重要数据丢 失。

#### 3.4.2.2 写主存储块

FMC 支持对主存储区的 16 位(半字)数据写入,可选择通过 Debug、BootLoader、程序在 SRAM 中运行、直接读取已擦除的页等方式判断是否擦除成功。

为保证写入正确,需要在写入前检查目的地址是否已经被擦除,若未被擦除,则写入数据无效并将 FMC\_STS 寄存器的 PEF 位置"1"。若目的地址存在写保护,则写入数据无效并触发一个写保护错误(FMC STS 的 WPEF 位置"1")。

### 3.4.2.3 读/写保护主存储块

闪存读/写保护用以防止非法读出/修改主存储区代码或数据,它由选项字节的读/写保护配置字节控制。对于 APM32F107 105xx 系列产品,读/写保护的基本单位是 2页(即 4KBytes)。

#### 读保护

可通过修改选项字节 READPROT 的值设置内部 Flash 保护级别。调试器一直连接 JTAG/SWD 接口设置读保护,需上电复位后生效;否则,系统电复位就能能有效。READPROT 值为除 0xA5 外的任意值时,开启读保护,无法读取主存储块的内容;READPROT 值为 0xA5 时,解除保护,可读取主存储块的内容;在解除读保护时会触发一个主存储块片擦除操作,以防止保护降级后的非法读取。

#### 写保护

可通过配置写保护选项字节 WRP0/1/2/3 的值来实现对主存储块对应的页进行写保护控制,写保护开启后,主存储区对应页的内容使用任何方式都不能被修改。

#### 3.4.2.4 解锁/锁定主存储块

如果 FMC\_CTRL1 被锁定,那么主存储块也会被锁定,因此,如果要对主存储块进行擦/写操作,需要先解锁 FMC CTRL1。

复位后 FMC 的 FMC\_CTRL1 会被硬件锁定,此时不能直接对 FMC\_CTRL1 进行写入操作,必须先按照正确的顺序向 FMC\_KEY 写入对应的值来解锁 FMC。 KEY 值如下:

- KEY1=0x45670123

- KEY2=0xCDEF89AB

错误的写入顺序或错误的值均会使程序进入硬件错误,而且此时 FMC 将被锁定,所有 FMC 操作均无效,直到下次复位才能解除。用户也可以通过向控制寄存器 2(FMC CTRL2)的 LOCK 位写"1"来软件锁定 FMC。

用户在每次 Flash 编程操作中必须按照 "Flash 解锁——用户编程——Flash 上 锁"的步骤进行,以避免在 Flash 编程操作结束后,因 Flash 未上锁而带来的用户 代码/数据被意外修改等风险。

#### 选项字节 3.4.3

#### 3.4.3.1 擦选项字节

支持擦除功能,正确的选项字节擦除(或选项字节写入操作)结束后, FMC STS 寄存器的 OCF 将会被置位,若开启了 OCIE 中断则将触发一个操作完 成中断。

#### 3.4.3.2 写选项字节

选项字节的8个可配置字节均支持写入功能。

#### 3.4.3.3 写保护选项字节

默认状态下,选项字节始终是可以读且被写保护。要想对选项字节块进行写操作 (编程/擦除) 首先要在 FMC OBKEY 中写入正确的键序列 (与上锁时一样), 随 后允许对选项字节块的写操作,FMC CTRL2 寄存器的 OBWEN 位标示允许写, 清除这位将禁止写操作。

#### 3.4.3.4 解锁/锁定选项字节

系统复位后选项字节默认处于锁定状态,只有进行正确的解锁操作才能修改选项 字节。选项字节解锁与闪存解锁不同点在 KEY 值写入的是 FMC OBKEY 寄存器 而不是 FMC KEY 寄存器。选项字节不支持"软件上锁",用户需要特别注意的是 每次修改选项字节的值后,需要系统复位才能使之生效。

#### 3.5 选项字节寄存器功能描述

选项字节为用户提供了一些可供选择的功能,它主要由8个可配置的字节和对应 的补码组成。在每次系统复位后,选项字节区将被重加载到 FMC OBCS 和 FMC WRTPROT 寄存器(选项字节只有每次被重加载到 FMC 后中才会生效)。 在重加载过程中,若出现某个可配置字节与它的反码不匹配问题,则将触发一个 选项字节错误(FMC OBCS 寄存器的 OBE 位置"1"),同时这个字节将会被置为

"0xFF"。选项字节区 16 字节的信息见下表。

| 地址          | 选项字节      | 初始值  | R/W | 功能描述                                                                                 |

|-------------|-----------|------|-----|--------------------------------------------------------------------------------------|

| 0x1FFF F800 | READPROT  | 0xA5 | R/W | 读保护配置                                                                                |

| 0x1FFF F801 | nREADPROT | 0x5A | R   | READPROT 补码                                                                          |

| 0x1FFF F802 | UOB       | 0xFF | R/W | 用户选项字节<br>位 0: WDTSEL<br>0: 硬件看门狗<br>1: 软件看门狗<br>位 1: nRSTSTOP<br>0: 进入 Stop 模式时产生复位 |

表格 9 选项字节

Page17 www.geehy.com

| 地址          | 选项字节   | 初始值  | R/W | 功能描述                             |

|-------------|--------|------|-----|----------------------------------|

|             |        |      |     | 1: 进入 Stop 模式时不产生复位              |

|             |        |      |     | 位 2: nRSTSTB                     |

|             |        |      |     | 0: 进入 Standby 模式时产生复位            |

|             |        |      |     | 1: 进入 Standby 模式时不产生复位 [3:7]: 保留 |

| 0x1FFF F803 | nUOB   | 0x00 | R   | UOB 补码                           |

| 0x1FFF F804 | Data0  | 0xFF | R/W | 用户数据字节 0                         |

| 0x1FFF F805 | nData0 | 0x00 | R   | Data0 补码                         |

| 0x1FFF F806 | Data1  | 0xFF | R/W | 用户数据字节 1                         |

| 0x1FFF F807 | nData1 | 0x00 | R   | Data1 补码                         |

| 0x1FFF F808 | WRP0   | 0xFF | R/W | 写保护配置 0                          |

| 0x1FFF F809 | nWRP0  | 0x00 | R   | WRP0 补码                          |

| 0x1FFF F80A | WRP1   | 0xFF | R/W | 写保护配置 1                          |

| 0x1FFF F80B | nWRP1  | 0x00 | R   | WRP1 补码                          |

| 0x1FFF F80C | WRP2   | 0xFF | R/W | 写保护配置 2                          |

| 0x1FFF F80D | nWRP2  | 0x00 | R   | WRP2 补码                          |

| 0x1FFF F80E | WRP3   | 0xFF | R/W | 写保护配置 3                          |

| 0x1FFF F80F | nWRP3  | 0x00 | R   | WRP3 补码                          |

注意: 当可配置字节和它的补码值为"0xFF"时,重加载过程中将不会再进行匹配验证

表格 10 主存储区写保护 WRPx 功能描述

| 产品容量                            | 功能描述                                                                                                                                                                                            |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APM32F107 105xx 系列产品<br>(2KB/页) | WRPx 中的每一个 bit 位控制主存储区 4KB(2 页)地址的写保护。<br>但第 62-127 页是同时提供保护。<br>0: 开启写保护<br>1: 未开启写保护<br>WRP0: 第 0-15 页<br>WRP1: 第 16-31 页<br>WRP2: 第 32-47 页<br>WRP3: Bit0-Bit6 控制第 48-61 页;Bit7 控制第 62-127 页 |

注意: Flash 读/写保护配置是互相独立的,解除写保护不会强制丢失主存储区的内容,而是原样保留。

# 3.6 FMC 寄存器地址映射

基地址: 0x40022000

表格 11 FMC 寄存器地址映射

| 寄存器名      | 描述      | 偏移地址 |

|-----------|---------|------|

| FMC_CTRL1 | 控制寄存器 1 | 0x00 |

| FMC_KEY   | 关键字寄存器  | 0x04 |

| 寄存器名        | 描述           | 偏移地址 |

|-------------|--------------|------|

| FMC_OBKEY   | 选项字节寄存器      | 0x08 |

| FMC_STS     | 状态寄存器        | 0x0C |

| FMC_CTRL2   | 控制寄存器 2      | 0x10 |

| FMC_ADDR    | 闪存地址寄存器      | 0x14 |

| FMC_OBCS    | 选项字节控制/状态寄存器 | 0x1C |

| FMC_WRTPROT | 写保护寄存器       | 0x20 |

# 3.7 FMC 寄存器功能描述

# 3.7.1 控制寄存器 1(FMC\_CTRL1)

偏移地址: 0x00

复位值: 0x0000 0030

| 位/域  | 名称    | R/W | 描述                                             |

|------|-------|-----|------------------------------------------------|

|      |       |     | 配置等待周期(Wait State Configure)                   |

|      |       |     | 000: 0 个等待周期,0<系统时钟≤24MHz                      |

| 2:0  | WS    | R/W | 001: 1个等待周期,24MHz<系统时钟≤48MHz                   |

|      |       |     | 010:2个等待周期,48MHz<系统时钟≤72MHz                    |

|      |       |     | 011: 3 个等待周期,72MHz<系统时钟≤96MHz                  |

|      |       |     | 使能 Flash 半周期访问(Flash Half Cycle Access Enable) |

| 3    | HCAEN | R/W | 0: 禁止                                          |

|      |       |     | 1: 使能                                          |

|      |       |     | 使能预取缓存区(Prefetch Buffer Enable)                |

| 4    | PBEN  | R/W | 0: 禁用                                          |

|      |       |     | 1: 使能                                          |

|      |       |     | 预取缓存区状态标志(Prefetch Buffer Status Flag)         |

| 5    | PBSF  | R   | 0: 处于关闭状态                                      |

|      |       |     | 1: 处于打开状态                                      |

| 31:6 |       |     | 保留                                             |

# 3.7.2 关键字寄存器 (FMC\_KEY)

偏移地址: 0x04

复位值: 0xXXXX XXXX

| 位/域  | 名称  | R/W | 描述                                                              |

|------|-----|-----|-----------------------------------------------------------------|

| 31:0 | KEY | W   | FMC 关键字(FMC Key)<br>写入这些位所表示的关键字可以解锁 FMC,这些位只能执行写操作,执行读操作时返回 0。 |

# 3.7.3 选项字节关键字寄存器(FMC\_OBKEY)

偏移地址: 0x08

复位值: 0xXXXX XXXX

| 位/域  | 名称    | R/W | 描述                                                                                |

|------|-------|-----|-----------------------------------------------------------------------------------|

| 31:0 | OBKEY | W   | 选项字节关键字(Option Byte Key)<br>写入这些位所表示的关键字可以解除选项字节写操作的锁定,这些位只<br>能执行写操作,执行读操作时返回 0。 |

# 3.7.4 状态寄存器 (FMC\_STS)

偏移地址: 0x0C 复位值: 0x0000 0000

| 位/域  | 名称    | R/W | 描述                                                                 |

|------|-------|-----|--------------------------------------------------------------------|

| 0    | BUSYF | R   | 忙碌标志(Busy Flag)<br>该位表示正在进行闪存操作,这些位只能执行写操作,执行读操作时<br>返回 0。         |

| 1    | 保留    |     |                                                                    |

| 2    | PEF   | PEF |                                                                    |

| 3    | 保留    |     |                                                                    |

| 4    | WPEF  | R/W | 写保护错误标志(Write Protection Error Flag)<br>当编程 FLASH 里写保护地址时,该位由硬件置位。 |

| 5    | OCF   | R/W | 操作完成标志(Operation Complete Flag)<br>当 FLASH 里的读/写操作完成时,由硬件置位。       |

| 31:6 |       |     | 保留                                                                 |

# 3.7.5 控制寄存器 2 (FMC\_CTRL2)

偏移地址: 0x10

复位值: 0x0000 0080

| 位/域 | 名称      | R/W | 描述                                                        |

|-----|---------|-----|-----------------------------------------------------------|

| 0   | PG      | R/W | 编程(Program)<br>该位置 1 进行 Flash 编程操作。                       |

| 1   | PAGEERA | R/W | 页擦除(Page Erase)<br>该位置 1 进行页擦除。                           |

| 2   | MASSERA | R/W | 整片擦除(Mass Erase)<br>该位置 1 进行整片擦除。                         |

| 3   | 保留      |     |                                                           |

| 4   | ОВР     | R/W | 编程选项字节(Option Byte Program)<br>该位置 1 进行选项字节编程操作。          |

| 5   | OBE     | R/W | 擦除选项字节(Option Byte Erase)<br>该位置 1 进行选项字节擦除操作。            |

| 6   | STA     | R/W | 开始进行擦除操作(Start Erase)<br>该位只能由软件置 1,在 STS_BUSYF 位清 0 时复位。 |

| 7   | LOCK    | R/W | 锁定(Lock)<br>该位只能写 1,该位置 1 表示 FMC 和 CTRL2 寄存器被锁定。          |

| 8   |         |     | 保留                                                        |

| 位/域   | 名称                                                                                                     | R/W | 描述                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------|

| 9     | OBWEN                                                                                                  | R/W | 使能选项字节写操作(Option Byte Write Enable)<br>当该位置 1 时,选项字节可以被编程。                          |

| 10    | ERRIE                                                                                                  | R/W | 使能错误中断(Error Interrupt Enable) 0: 禁止中断 1: 使能中断 当 STS_PEF=1 或 STS_WPEF=1 时,设置该位产生中断。 |

| 11    | 保留                                                                                                     |     |                                                                                     |

| 12    | OCIE PKW 使能操作完成中断(Operation Complete Interrupt Enable) 0: 操作完成中断禁用 1: 操作完成中断使能 当 STS_OCF=1 时,设置该位产生中断。 |     |                                                                                     |

| 31:13 | 保留                                                                                                     |     |                                                                                     |

# 3.7.6 地址寄存器 (FMC\_ADDR)

偏移地址: 0x14

复位值: 0x0000 0000

该寄存器由硬件修改为当前/最后使用的地址;页擦除时,需通过软件配置该寄存器。

| 位/域  | 名称   | R/W | 描述                                                                    |

|------|------|-----|-----------------------------------------------------------------------|

| 31:0 | ADDR | W   | Flash 地址(Flash Address)<br>在进行编程操作时,该位写入要编程的地址,在进行页擦除时,该位<br>写入要擦除的页。 |

# 3.7.7 选项字节控制/状态寄存器(FMC\_OBCS)

偏移地址: 0x1C

复位值: 0x03FF FFFC

该寄存器的复位值与写入选项字节中的数值有关; OBE 位的复位值与加载的选项字节数值和它的反码是否一致的结果有关。

| 位/域   | 名称       | R/W | 描述                                                                                                          |

|-------|----------|-----|-------------------------------------------------------------------------------------------------------------|

| 0     | OBE      | R   | 选项字节错误(Option Byte Error)  1: 所加载的选项字节和它的补码不匹配,选项字节和它的补码强制写入 0xFF                                           |

| 1     | READPROT | R   | 读保护(Read Protect)<br>1:表示闪存处于读保护状态                                                                          |

| 9:2   | UOB      | R   | 用户选项字节(User Option Byte)<br>这里包含 OBL 加载的用户选择字节<br>位 2: WDTSEL<br>位 3: RSTSTOP<br>位 4: RSTSTDB<br>位[9:5]: 未用 |

| 17:10 | DATA0    | R   | Data0                                                                                                       |

| 25:18 | DATA1    | R   | Data1                                                                                                       |

| 31:26 |          |     | 保留                                                                                                          |

# 3.7.8 写保护寄存器(FMC\_WRTPROT)

偏移地址: 0x20

复位值: 0xFFFF FFFF

| 位/域  | 名称      | R/W | 描述                                   |

|------|---------|-----|--------------------------------------|

| 31:0 | WRTPROT | R   | 写保护(Write Protect)<br>0: 有效<br>1: 无效 |

# 4 复位与时钟管理(RCM)

# 4.1 术语全称、缩写描述

表格 12 术语全称、缩写描述

| 中文全称    | 英文全称                       | 英文缩写   |

|---------|----------------------------|--------|

| 复位与时钟管理 | Reset and Clock Management | RCM    |

| 复位      | Reset                      | RST    |

| 上电复位    | Power-On Reset             | POR    |

| 掉电复位    | Power-Down Reset           | PDR    |

| 高速外部时钟  | High Speed External Clock  | HSECLK |

| 低速外部时钟  | Low Speed External Clock   | LSECLK |

| 高速内部时钟  | High Speed Internal Clock  | HSICLK |

| 低速内部时钟  | Low Speed Internal Clock   | LSICLK |

| 锁相环     | Phase Locked Loop          | PLL    |

| 主要时钟输出  | Main Clock Output          | MCO    |

| 校准      | Calibrate                  | CAL    |

| 调整      | Trim                       | TRIM   |

| 唤醒      | Wakeup                     | WUP    |

| 自动唤醒    | Automatic Wakeup           | AWUP   |

| 备份      | Backup                     | BAKP   |

| 低功耗     | Low Power                  | LPWR   |

| 时钟安全系统  | Clock Security System      | CSS    |

| 不可屏蔽中断  | Non Maskable Interrupt     | NMI    |

# 4.2 复位功能描述

支持的复位分为三类:系统复位、电源复位、备份区域复位三种复位形式。

# 4.2.1 系统复位

### 4.2.1.1 "系统复位"复位源

复位源分为外部复位源、内部复位源。

外部复位源:

● NRST 引脚上的低电平。

内部复位源:

● 窗口看门狗终止计数(WWDT 复位)

- 独立看门狗终止计数 (IWDT 复位)

- 软件复位(SW 复位)

- 低功耗管理复位

- 电源复位

以上任一事件发生时,都能产生一个系统复位。另外,可以通过查看 RCM\_CSTS(控制/状态寄存器)中的复位标志位识别复位事件来源。

一般来说,系统复位时,会将除了RCM\_CSTS(控制/状态寄存器)的复位标志位和备份区域中的寄存器以外的所有寄存器复位到复位状态。

#### 软件复位

将 Arm<sup>®</sup> Cortex<sup>®</sup>-M3 中断应用和复位控制寄存器中的 SYSRESETREQ 置"1"时,可实现软件复位。

### 低功耗管理复位

低功耗管理复位的产生有两种情况,一种是进入待机模式时,另一种是进入停止模式时。在这两种情况下,如果把用户选择字节中的 RSTSTDB 位(待机模式时)或 RSTSTOP 位(停止模式时)清零,系统将被复位而不是进入待机模式或停止模式。

有关用户选择字节的详细信息,请参考"Flash 存储器"。

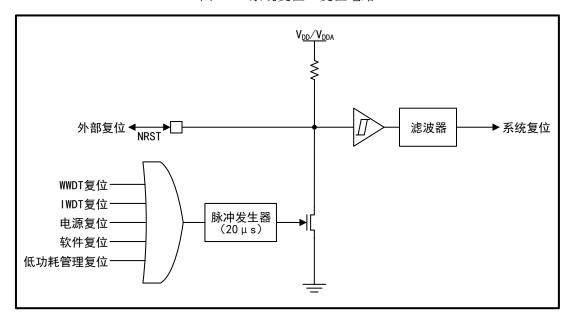

### 4.2.1.2 "系统复位"复位电路

复位源均作用于 NRST 引脚,该引脚并在复位过程中保持低电平。

内部复位源通过脉冲发生器在 NRST 引脚产生延时至少 20 µs 的脉冲,引起 NRST 保持电平产生复位;外部复位源则直接将 NRST 引脚电平拉低产生复位。

"系统复位"复位电路见下图。

图 2 "系统复位"复位电路

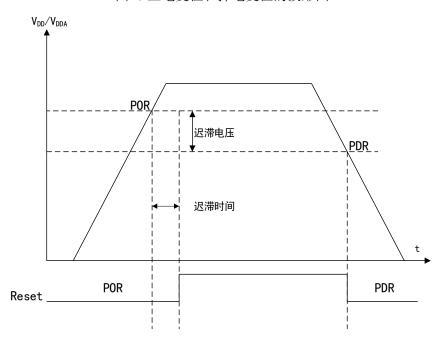

### 4.2.2 电源复位

### "电源复位"复位源

"电源复位"复位源如下:

- 上电复位 (POR 复位)

- 掉电复位 (PDR 复位)

- 从待机模式唤醒

以上任一事件发生时,产生电源复位。

电源复位将复位除了备份区域外的所有寄存器。

# 4.2.3 备份域复位

### "备份域复位"复位源

"备份域复位"复位源如下:

- 软件复位,设置 RCM BDCTRL(备份域控制寄存器)中的 BDRST 位

- 在 V<sub>DD</sub> 和 V<sub>BAT</sub> 掉电时, V<sub>DD</sub> 或 V<sub>BAT</sub> 上电

以上任一事件发生时,产生备份域复位。

备份区域复位拥有两个专门的复位,它们只影响备份区域。

# 4.3 时钟管理功能描述

整个系统的时钟源有: HSECLK、LSECLK、HSICLK、LSICLK、PLL。关于时钟源的特性,请参考数据手册的"电气特性"中的相关章节。

### 4.3.1 外部时钟源

外部时钟信号包括 HSECLK (高速外部时钟信号) 和 LSECLK (低速外部时钟信号)。

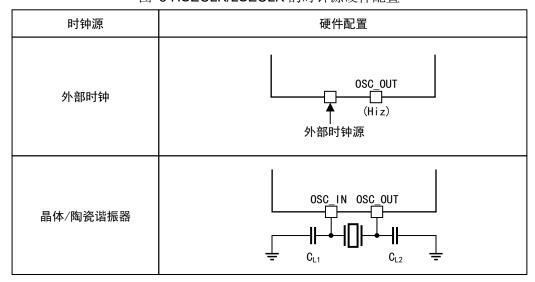

外部的时钟源有两种:

- 外部晶体/陶瓷谐振器

- 用户外部时钟

两种时钟源的硬件配置如下图所示。

图 3 HSECLK/LSECLK 的时钟源硬件配置

为了减少时钟输出的失真和缩短启动稳定时间,晶体/陶瓷谐振器和负载电容器必须尽可能地靠近振荡器引脚。负载电容( $C_{L1}$ 、 $C_{L2}$ )的值必须根据所选择的振荡器来调整。

### 4.3.1.1 HSECLK 高速外部时钟信号

HSECLK 时钟信号由 HSECLK 外部晶体/陶瓷谐振器和 HSECLK 外部时钟两种时钟源产生。

表格 13 产生 HSECLK 的时钟源

| 名称                   | 说明                                                                                                                                                                                                            |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 外部时钟源<br>(HSECLK 旁路) | 通过 OSC_IN 引脚给 MCU 提供时钟。<br>信号可以有普通的函数信号发送器(调试时)、晶体振荡器、其它信号发生器产生;波形可以是 50%占空比的方波、正弦波或三角波,最高频率可达 25MHz。<br>硬件连接上,必须连到 OSC_IN 引脚,同时保证 OSC_OUT 引脚悬空;MCU<br>配置上,用户可通过设置在 RCM_CTRL 中的 HSEBCFG 和 HSEEN 位来选择<br>这一模式。 |

| 名称                        | 说明                                                                                                                                                                                                                          |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 外部晶体/陶瓷谐振器<br>(HSECLK 晶体) | 通过谐振器给 MCU 提供时钟,谐振器包括晶体谐振器、陶瓷谐振器。 频率范围是 3-25MHz。 需要 OSC_IN、OSC_OUT 连接谐振器,可以通过设置 RCM_CTRL 中的 HSEEN 位,启动和关闭。 在时钟控制寄存器 RCM_CTRL 中的 HSERDYFLG 位用来指示高速外部振荡器是否稳定。在启动后,直到这一位被硬件置"1",时钟才被释放出来。如果在 RCM_INT(时钟中断寄存器)中允许产生中断,将会产生相应中断。 |

#### 4.3.1.2 LSECLK 低速外部时钟信号

LSECLK 时钟信号由 LSECLK 外部晶体/陶瓷谐振器和 LSECLK 外部时钟两种时钟源产生。

名称 通过 OSC32 IN 引脚给 MCU 提供时钟。 信号可以有普通的函数信号发送器(调试时)、晶体振荡器、其它信号发生器产 生;波形可以是 50%占空比的方波、正弦波或三角波,信号频率需为 外部时钟源 32.768kHz。 (LSECLK 旁路) 硬件连接上,必须连到 OSC32 IN 引脚,同时保证 OSC32 OUT 引脚悬空; MCU 配置上,用户可通过设置在 RCM BDCTRL 里的 LSEBCFG 和 LSEEN 位来选择这个模式。 通过谐振器给 MCU 提供时钟,谐振器包括晶体谐振器、陶瓷谐振器。 频率是 32.768kHz。 需要 OSC32 IN、OSC32 OUT 连接谐振器,可以通过在 RCM BDCTRL 里 外部晶体/陶瓷谐振器 的 LSEEN 位启动和关闭。 (LSECLK 晶体) 在 RCM\_BDCTRL 里的 LSERDYFLG 指示 LSECLK 晶体振荡是否稳定。在启 动阶段,直到这个位被硬件置"1"后,LSECLK时钟信号才被释放出来。如果 在时钟中断寄存器里被允许, 可产生中断申请。

表格 14 产生 LSECLK 的时钟源

### 4.3.2 内部时钟源

内部时钟包含 HSICLK(高速内部时钟信号)和 LSICLK(低速内部时钟信号)。

#### 4.3.2.1 HSICLK 高速内部时钟信号

HSICLK 时钟信号由内部 8MHz 的 RC 振荡器产生。

不同芯片的 RC 振荡器频率不同,且同一颗芯片随着温度、电压的变化也会存在差异;每个芯片的 HSICLK 时钟频率在出厂前已经被厂家校准到 1%(25℃、V<sub>DD</sub>=V<sub>DDA</sub>=3.3V),系统复位时,工厂校准值被装载到 RCM\_CTRL 的 HSICAL 位中;另外,用户可以依据现场的应用环境(温度、电压),通过设置 RCM\_CTRL中的 HSITRM 作进一步的频率调整。

HSIRDYFLG 位可以用来指示 HSICLK RC 振荡器是否稳定。在时钟启动过程中,直到 HSIRDYFLG 位被硬件置 1,HSICLK RC 输出时钟才被释放。HSICLK RC 可由 RCM CTRL 中的 HSIEN 位来启动或关闭。

与 HSECLK 晶体振荡器相比, RC 振荡器能够在不需要任何外部器件的条件下提供系统时钟;它的启动时间比 HSECLK 晶体振荡器短;即使在校准之后,其时

钟频率精度仍不如 HSECLK 晶体振荡器。

### 4.3.2.2 LSICLK 低速内部时钟信号

#### LSICLK 主要特征

LSICLK 由 RC 振荡器产生,范围是 40kHz(30kHz 和 60kHz 之间。随着温度、电压的变化,频率也会产生变化。可以在停机和待机模式下保持运行,为独立看门狗和自动唤醒单元提供时钟。

LSICLK 可以通过 RCM\_CSTS 的 LSIEN 位来启动或关闭。在 RCM\_CSTS 里的 LSIRDYFLG 位指示低速内部振荡器是否稳定。在启动阶段,直到这个位被硬件 设置为"1"后,时钟才被释放。如果在 RCM\_INT 里被允许,将产生 LSICLK 中断申请。

### LSICLK 校准

校准 LSICLK 振荡器的目的是为了补偿其频率偏移,校准后能够得到一定精度的 RTC 时钟基数以及 IWDT 的超时时间。

首先,将 TMR5 的通道 4 设置为输入捕获模式,连接 LSICLK 时钟并测量其时钟频率,然后以 HSECLK 时钟频率为精度保证,根据需要的 RTC 时间基数和 IWDT 的超过时间,设置 RTC 的 20 位预分频器。

# 4.3.3 PLL 锁相环

主锁相环 PLL1 可以用来倍频 HSICLK/2,或者是分频后的 HSECLK 或 PLL2CLK。

PLL2 和 PLL3 的输入源是分频后的 HSECLK。

时钟源和倍频因子应在被激活前完成选择,一旦 PLL1/2/3 被激活,选择将不能改变。

在切换时钟源时,要确保选择了新的时钟源才能关闭之前的时钟源。

当 PLL 准备就绪且 PLL 中断在 RCM INT 里被允许时, PLL 可发出中断申请。

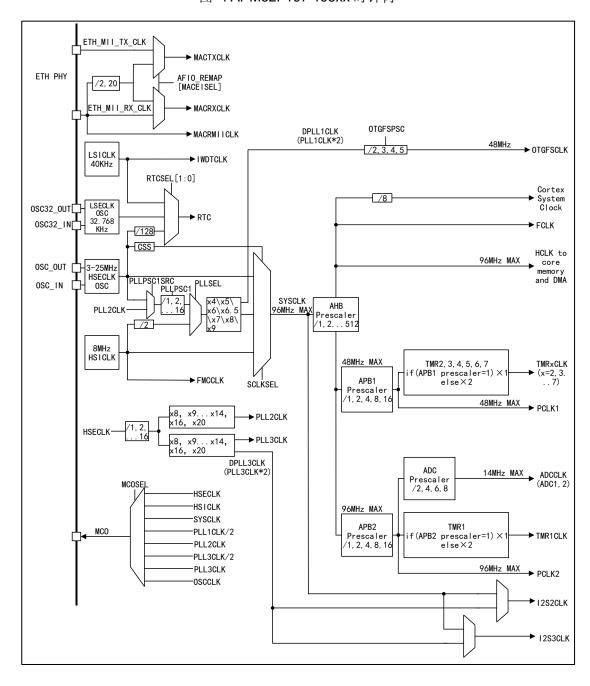

### 4.3.4 时钟树

图 4 APM32F107 105xx 时钟树

#### 注意:

- (1) HCLK 是指 AHB 时钟。

- (2) PCLK1, PCLK2 分别是指连接 APB1, APB2 的外设的时钟信号。

- (3) FCLK 是 Arm® Cortex®-M3 的运行时钟。

- (4) 可通过多个预分频器配置 AHB、APB2(高速 APB)和 APB1(低速 APB)域的频率。其中,AHB 和 APB2 域的最大频率是 96MHz,而 APB1 域的最大允许频率是 48MHz。

- (5) 当 HSICLK 作为 PLL 时钟的输入时,系统时钟能得到的最大频率是 36MHz。

- (6) 当使用 USB OTG FS 时,必须提供 48MHz 的时钟信号。

- (7) 当需要运行连接 AHB, APB 的外设时,都需要开启相应的使能端,使外设获得时钟信号。

- (8) SysTick (系统定时器) 可由 HCLK 8 分频后的时钟信号提供,通过对 SysTick 控制与状态寄存器的设置,可选择不同时钟源。

- (9) 所有 TMRxCLK (定时器时钟) 频率分配由硬件按以下 2 种情况自动设置:

- 如果相应的 APB 预分频系数是 1,定时器的时钟频率与所在 APB 总线频率一致。

- 否则, 定时器的时钟频率被设为与其相连的 APB 总线频率的 2 倍。

- (10) 其中, TMRx (x=2,3,4,5,6,7) 时钟信号通过 PCLK1 分频后得到, TMR1 时钟信号通过 PCLK2 分频后得到。

### 4.3.5 RTC 的时钟源选择

通过设置 RCM\_BDCTRL 里的 RTCSRCSEL 位可选择 HSECLK/128、LSECLK 或 LSICLK 作为 RTCCLK 时钟源。只有备份域复位时,时钟源的选择可以改变。

由于 LSECLK 在备份域里,HSECLK、LSICLK 不在备份域内,因此,选择不同的时钟源,RTC 的工作情况存在差异,具体情况见下表:

| 农怕 13 110 选择/国的扩播的 110 的工作情况 |                                                                                                                 |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| 时钟源                          | 工作情况                                                                                                            |  |  |

| LSECLK 被选为 RTC 时钟            | 只要 V <sub>BAT</sub> 维持供电,尽管 V <sub>DD</sub> 供电被切断,RTC 仍继续工作                                                     |  |  |

| LSICLK 被选为自动唤醒单元时<br>钟       | 如果 Vod 供电被切断,AWUP 状态不能被保证。                                                                                      |  |  |

| HSECLK/128 作为 RTC 时钟         | 如果 V <sub>DD</sub> 供电被切断或内部电压调压器被关闭(1.3V 域的供电被切断),则 RTC 状态不确定,故必须设置 PMU_CTRL(电源控制寄存器)的 BPWEN 位(取消后备区域的写保护)为"1"。 |  |  |

表格 15 RTC 选择不同时钟源时 RTC 的工作情况

#### 4.3.6 IWDT 的时钟源选择

当 IWDT(独立看门狗)启动时,LSICLK 振荡器将被强制打开,等到稳定后把时钟信号供给 IWDT。LSICLK 在被强制打开后,将一直处于打开状态,不能被关闭。

## 4.3.7 MCO 的时钟源选择

当相应的 GPIO 端口寄存器被配置为对应功能时,可通过配置 RCM\_CFG(时钟配置寄存器)中的 MCOSEL 选择时钟信号输出到 MCO 引脚。具体时钟信号可参考时钟树或 MCOSEL 位说明。

### 4.3.8 SYSCLK 的时钟源选择

当进行系统复位后,HSICLK 振荡器被选作系统时钟,且不能被停止。如果要切换 SYSCLK 时钟源,必须要等目标时钟源准备就绪(即目标时钟源稳定)。目标时钟源可以是 HSECLK、PLLCLK。

RCM CFG 的状态位可指示已准备好的时钟和已被选作的 SYSCLK 时钟源。

### 4.3.9 CSS 时钟安全系统

为了防止由于外部晶振短路导致 MCU 无法正常运行的情况,MCU 可通过软件激活 CSS 时钟安全系统。安全系统被激活后,如果 HSECLK 振荡器直接或间接(作为 PLL 输入时钟且 PLL 作为系统时钟)被用作系统时钟,那么当 HSECLK 时钟发生故障时,外部 HSECLK 振荡器被关闭,系统时钟自动切换至 HSICLK,此时选择 HSECLK 为时钟输入且作为系统时钟输入源的 PLL 也会被关闭。

注意: CSS 被软件激活并且 HSECLK 时钟出现故障时,会产生 CSS 中断和 NMI(不可屏蔽中断)。由于 CSS 中断被清除前 NMI 不断被执行,所以需要设置 RCM\_INT 寄存器里的 CSSIF 位来清除中断。

# 4.4 寄存器地址映射

寄存器名 描述 偏移地址 RCM\_CTRL 0x00 时钟控制寄存器 RCM\_CFG1 0x04 时钟配置寄存器 1 80x0 RCM INT 时钟中断寄存器 RCM APB2RST APB2 外设复位寄存器 0x0C RCM APB1RST APB1 外设复位寄存器 0x10 AHB 外设时钟使能寄存器 0x14 RCM AHBCLKEN RCM APB2CLKEN APB2 外设时钟使能寄存器 0x18 RCM APB1CLKEN APB1 外设时钟使能寄存器 0x1C RCM\_BDCTRL 备份域控制寄存器 0x20 RCM CSTS 0x24 控制/状态寄存器 RCM AHBRST 0x28 AHB 外设复位寄存器 RCM CFG2 时钟配置寄存器 2 0x2C

表格 16 RCM 寄存器地址映射

# 4.5 寄存器功能描述

# 4.5.1 时钟控制寄存器(RCM\_CTRL)

偏移地址: 0x00

复位值: 0x0000 XX83, X代表未定义

访问: 以字,半字和字节形式访问, 无等待周期

| 位/域 | 名称    | R/W | 描述                                                                                                                                                                                                         |

|-----|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | HSIEN | R/W | 使能高速内部时钟(High Speed Internal Clock Enable)由软件置 1 或清 0。 HSICLK 是 RC 振荡器,以下条件中的一个出现时,会硬件置 1: 上电启动、软件复位、从待机模式唤醒、停机模式唤醒、外部高速时钟源(作为系统时钟的时钟源时)发生故障。当 HSICLK 作为系统时钟源或通过 PLL1 提供系统时钟时,该位不能清 0。 0: 关闭 HSICLK RC 振荡器 |

| 位/域   | 名称         | R/W | 描述                                                                                                                                             |

|-------|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|

|       |            |     | 1: 开启 HSICLK RC 振荡器                                                                                                                            |

| 1     | HSIRDYFLG  | R   | 高速内部时钟就绪标志(High Speed Internal Clock Ready Flag)<br>0: HSICLK RC 振荡器未稳定<br>1: HSICLK RC 振荡器已稳定                                                 |

| 2     |            |     | 保留                                                                                                                                             |

| 7:3   | HSITRM     | R/W | 调整高速内部时钟(High Speed Internal Clock Trim)<br>产品在出厂时会校准到 8MHz±1%,但随着温度、电压的变化而变<br>化,可通过 HSITRM 调整 HSICLK RC 振荡器的频率。                              |

| 15:8  | HSICAL     | R   | 校准内部高速时钟(High Speed Internal Clock Calibrate)<br>在系统启动时,会将校准参数自动写入该寄存器。                                                                        |

| 16    | HSEEN      | R/W | 使能高速外部时钟(High Speed External Clock Enable)进入待机或停机模式时,该位由硬件清 0,关闭 HSECLK; 当 HSECLK 作为系统时钟源或通过 PLL1 提供系统时钟时,该位不能清 0。  0: HSECLK 关闭  1: HSECLK 开启 |

| 17    | HSERDYFLG  | R   | 高速外部时钟就绪标志(High Speed External Clock Ready Flag)<br>HSECLK 稳定后有硬件置 1,软件清 0。<br>0: HSECLK 未稳定<br>1: HSECLK 已稳定                                  |

| 18    | HSEBCFG    | R/W | 配置高速外部时钟旁路模式(High Speed External Clock Bypass Configure)<br>旁路模式指外部时钟作为 HSECLK 时钟源,否则谐振器作为<br>HSECLK 时钟源。<br>0: 非旁路模式<br>1: 旁路模式               |

| 19    | CSSEN      | R/W | 使能时钟安全系统(Clock Security System Enable)<br>0:禁止<br>1:使能(当 HSECLK 振荡器准备就绪)                                                                       |

| 23:20 |            |     | 保留                                                                                                                                             |

| 24    | PLL1EN     | R/W | 使能 PLL1 (PLL1 Enable) 当进入特机和停止模式时,该位由硬件清零; 当 PLL1CLK 已配置为 (或者配置过程中)系统时钟的时钟源,该位不能清 0; 其他情况可由软件置 1 或清 0。 0: PLL1 关闭 1: PLL1 使能                   |

| 25    | PLL1RDYFLG | R   | PLL1 时钟就绪标志(PLL1 Clock Ready Flag) PLL1 锁定后由硬件置 1。 0: PLL1 未锁定 1: PLL1 锁定                                                                      |

| 26    | PLL2EN     | R/W | 使能 PLL2(PLL2 Enable)<br>当进入待机和停止模式时,该位由硬件清零;当 PLL2CLK 已配置为<br>系统时钟的时钟源,该位不能清 0。<br>0:PLL2 关闭<br>1:PLL2 使能                                      |

| 位/域   | 名称         | R/W | 描述                                                                                  |

|-------|------------|-----|-------------------------------------------------------------------------------------|

| 27    | PLL2RDYFLG | R   | PLL2 时钟就绪标志(PLL2 Clock Ready Flag) PLL2 锁定后由硬件置 1。 0: PLL2 未锁定 1: PLL2 锁定           |

| 28    | PLL3EN     | R/W | 使能 PLL3 (PLL3 Enable)<br>通过软件置位或清除。当进入待机和停止模式时,该位由硬件清零。<br>0: PLL3 关闭<br>1: PLL3 使能 |

| 29    | PLL3RDYFLG | R   | PLL3 时钟就绪标志(PLL3 Clock Ready Flag)<br>PLL3 锁定后由硬件置 1。<br>0: PLL3 未锁定<br>1: PLL3 锁定  |

| 31:30 | 保留         |     |                                                                                     |

# 4.5.2 时钟配置寄存器 1 (RCM\_CFG1)

偏移地址: 0x04

复位值: 0x0000 0000

此寄存器所有位都由软件置位或清零。

访问: 以字,半字和字节形式访问,0到2个等待周期。

只有当访问发生在时钟切换时,才会插入1或2个等待周期。

| 位/域 | 名称         | R/W | 描述                                                                                                                                                                                                                                                  |

|-----|------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | SCLKSEL    | R/W | 选择系统时钟时钟源(System Clock Source Select)选择系统时钟源。 在从停止或待机模式中返回时或直接或间接作为系统时钟的 HSE 出现故障时,由硬件强制选择 HSICLK 作为系统时钟(如果时钟安全系统已经启动) 00: HSICLK 作为系统时钟 01: HSECLK 作为系统时钟 10: PLL1CLK 作为系统时钟                                                                       |

| 3:2 | SCLKSELSTS | R   | 系统时钟时钟源选择状态(System Clock Selection Status)<br>指示哪一个时钟源被作为系统时钟。<br>00: HSICLK 作为系统时钟<br>01: HSECLK 作为系统时钟<br>10: PLL1CLK 输出作为系统时钟<br>11: 不可用                                                                                                         |

| 7:4 | AHBPSC     | R/W | 配置 AHB 时钟预分频(AHB Clock Prescaler Factor Configure)<br>控制 AHB 时钟的预分频系数。<br>0xxx: SYSCLK 不分频<br>1000: SYSCLK 2 分频<br>1001: SYSCLK 4 分频<br>1010: SYSCLK 8 分频<br>1011: SYSCLK 16 分频<br>1100: SYSCLK 64 分频<br>1101: SYSCLK 128 分频<br>1110: SYSCLK 256 分频 |

| 位/域   | 名称            | R/W      | 描述                                                                        |

|-------|---------------|----------|---------------------------------------------------------------------------|

|       |               |          | 1111: SYSCLK 512 分频                                                       |

|       |               |          | 注意: 当 AHB 时钟的预分频系数大于 1 时,必须开启预取缓冲器。                                       |

|       |               |          | 若要使用以太网,则 AHB 的时钟频率至少要达到 25MHz。                                           |

|       |               |          | 配置 APB1 时钟预分频系数(APB1 Clock Prescaler Factor                               |

|       |               |          | Configure )                                                               |

|       |               |          | 来控制低速 APB1 时钟(PCLK1)的预分频系数。                                               |

|       |               |          | 警告:软件必须保证 APB1 时钟频率不超过 48MHz。                                             |

| 10:8  | APB1PSC       | R/W      | 0xx: HCLK 不分频                                                             |

|       |               |          | 100: HCLK 2 分频                                                            |

|       |               |          | 101: HCLK 4 分频                                                            |

|       |               |          | 110: HCLK 8 分頻                                                            |

|       |               |          | 111: HCLK 16 分频                                                           |

|       |               |          | 配置 APB2 时钟预分频系数(APB2 Clock Prescaler Factor)                              |

|       |               |          | 控制高速 APB2 时钟(PCLK2)的预分频系数。                                                |

|       |               |          | 0xx: HCLK 不分频;                                                            |

| 13:11 | APB2PSC       | R/W      | 100: HCLK 2 分频                                                            |

|       |               |          | 101: HCLK 4 分频                                                            |

|       |               |          | 110: HCLK 8 分频                                                            |

|       |               |          | 111: HCLK 16 分频                                                           |

|       |               |          | 配置 ADC 时钟预分频系数(ADC 时钟 Prescaler Factor                                    |

|       |               |          | Configure )                                                               |

|       |               |          | 确定 ADC 时钟频率                                                               |

| 15:14 | ADCPSC        | R/W      | 00: PCLK2 2 分頻后作为 ADCCLK                                                  |

|       |               |          | 01: PCLK2 4 分頻后作为 ADCCLK                                                  |

|       |               |          | 10: PCLK2 6 分頻后作为 ADCCLK                                                  |

|       |               |          | 11: PCLK2 8 分频后作为 ADCCLK                                                  |

|       |               |          | 选择 PLL1 时钟源(PLL1 Clock Source Select)                                     |

| 40    | DI 1 40 DOOE! | D 44/    | 选择 PLL1 输入时钟源。                                                            |

| 16    | PLL1SRCSEL    | R/W      | 0: HSICLK RC 振荡器时钟经 2 分频后作为 PLL1 输入时钟                                     |

|       |               |          | 1: HSECLK 作为 PLL1 输入时钟                                                    |

|       |               |          | 注:只能在关闭 PLL1 时才能写入此位。                                                     |

|       |               |          | PLLPSC1 的低位(LSB of PLLPSC1 )                                              |

| 17    | PLLPSC1L      | R/W      | 此位是 RCM_CFG2[PLLPSC1]的最低位。可以通过软件来设置此位的使,此位上 RCM_CFG2[9]具目,位,FDIAT设置AC的基本。 |

| ''    | PLLPSCIL      | IT/VV    | 的值,此位与 RCM_CFG2[0]是同一位,所以修改这两个位的其中一个都会影响另一个位。                             |

|       |               |          | 注: 只能在关闭 PLL1 时才能写入此位。                                                    |

|       |               |          | 配置 PLL1 倍频系数(PLL1 Multiplication Factor Configure)                        |

|       |               |          | 一                                                                         |

|       |               |          | 000x: 保留                                                                  |

|       |               |          | 000X:                                                                     |

|       |               |          | 0010: T LETOLK + T J J H H H H H H H H H H H H H H H H H                  |

| 21:18 | PLL1MULCFG    | R/W      | 0100: PLL1CLK 6 倍频输出                                                      |

| 21.10 |               |          | 0101: PLL1CLK 7 倍频输出                                                      |

|       |               |          | 0110: PLL1CLK 8 倍频输出                                                      |

|       |               |          | 0111: PLL1CLK 9 倍频输出                                                      |

|       |               |          | 10xx: 保留                                                                  |

|       |               |          | 1100: 保留                                                                  |

|       | <u> </u>      | <u> </u> |                                                                           |

| 位/域   | 名称       | R/W | 描述                                                         |

|-------|----------|-----|------------------------------------------------------------|

|       |          |     | 1101: PLL1CLK 6.5 倍频输出                                     |

|       |          |     | 111x: 保留                                                   |

|       |          |     | 注意: PLL1CLK 的输出频率不能超过 96MHz。                               |

|       |          |     | 配置 OTG_FS 的预分频系数(USB OTG_FS Prescaler Factor<br>Configure) |

|       |          |     | 通过配置此位来产生 48MHz 的 OTG_FS 时钟。                               |

|       | OTGFSPSC | R/W | 在使能 OTG_FS 时钟之前,必须保证该位已经有效。如果 OTG_FS 时钟被使能,该位不能被清零。        |

| 23:22 |          |     | 00: DPLL1CLK(PLL1CLKx2)3分频后作为OTG_FS时钟                      |

|       |          |     | 01: DPLL1CLK(PLL1CLKx2)2 分频后作为OTG_FS 时钟                    |

|       |          |     | 10: DPLL1CLK(PLL1CLKx2) 4 分频后作为 OTG_FS 时钟                  |

|       |          |     | 11: DPLL1CLK(PLL1CLKx2) 5 分频后作为 OTG_FS 时钟                  |

|       |          |     | 注意:(1) OTG_FS 时钟频率必须为 48MHz。                               |

|       |          |     | (2) 第23位 可写不可读                                             |

|       |          |     | 选择主时钟输出(Main Clock Output Select)                          |

|       |          |     | 由软件置位或清零。                                                  |

|       |          |     | 00xx: 没有时钟输出                                               |

|       |          |     | 0100: 系统时钟(SYSCLK)输出                                       |

|       |          |     | 0101: 内部 RC 振荡器时钟(HSICLK)输出                                |

|       |          |     | 0110:外部振荡器时钟(HSECLK)输出                                     |

|       | MCOSEL   | R/W | 0111: PLL1CLK 2 分频后输出                                      |

| 27:24 |          |     | 1000: PLL2CLK 输出                                           |

|       |          |     | 1001: PLL3CLK 2 分频后输出                                      |

|       |          |     | <b>1010: OSCCLK</b> 输出(供给以太网)                              |

|       |          |     | 1011: PLL3CLK 输出(供给以太网)                                    |

|       |          |     | 其他:保留                                                      |

|       |          |     | 注意: 1.该时钟输出在启动或者切换 MCO 时钟源时可能会被截断。                         |

|       |          |     | 2.系统时钟信号输出至 MCO 引脚时,应保证输出时钟频率不超过 50MHz(I/O 口最高频率)。         |

| 31:28 | 保留       |     |                                                            |

# **4.5.3** 时钟中断寄存器(RCM\_INT)

偏移地址: 0x08

复位值: 0x0000 0000

访问: 以字,半字和字节形式访问, 无等待周期。

| 位/域 | 名称        | R/W | 描述                                                                                                                                                           |

|-----|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | LSIRDYFLG | R   | LSICLK 就绪中断标志(LSICLK Ready Interrupt Flag)<br>在内部低速时钟就绪且 LSIRDYEN 位被置 1 时,由硬件置 1。<br>由软件通过将 LSIRDYCLR 位置 1 来清 0 此位。<br>0: 无 LSICLK 就绪中断<br>1: 发生 LSICLK 就绪中断 |

| 1   | LSERDYFLG | R   | LSECLK 就绪中断标志(LSECLK Ready Interrupt Flag)<br>在外部低速时钟就绪且 LSERDYEN 位被置 1 时,由硬件置 1。<br>由软件通过将 LSERDYCLR 位置 1 来清 0 此位。<br>0: 无 LSECLK 就绪中断<br>1: 发生 LSECLK 就绪中断 |

| 位/域 | 名称         | R/W | 描述                                                                                                                                                                      |

|-----|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | HSIRDYFLG  | R   | HSICLK 就绪中断标志(HSICLK Ready Interrupt Flag)<br>在内部高速时钟就绪且 HSIRDYEN 位被置 1 时,由硬件置 1。<br>由软件通过将 HSIRDYCLR 位置 1 来清 0 此位。<br>0: 无 HSICLK 就绪中断<br>1: 发生 HSICLK 就绪中断            |

| 3   | HSERDYFLG  | R   | HSECLK 就绪中断标志(HSECLK Ready Interrupt Flag)<br>在外部低速时钟就绪且 HSERDYCLR 位被置 1 时,由硬件置 1。<br>由软件通过将 HSERDYCLR 位置 1 来清 0 此位。<br>0: 无 HSECLK 就绪中断<br>1: 发生 HSECLK 就绪中断           |

| 4   | PLL1RDYFLG | R   | PLL1 就绪中断标志(PLL1 Ready Interrupt Flag)<br>在 PLL1 就绪且 PLL1RDYEN 位被置 1 时,由硬件置 1。<br>由软件通过将 PLL1RDYCLR 位置 1 来清 0 此位。<br>0: 无 PLL1 上锁产生的时钟就绪中断<br>1: PLL1 上锁导致时钟就绪中断        |

| 5   | PLL2RDYFLG | R   | PLL2 就绪中断标志(PLL2 Ready Interrupt Flag)<br>在 PLL2 就绪且 PLL2RDYEN 位被置 1 时,由硬件置 1。<br>由软件通过将 PLL2RDYCLR 位置 1 来清 0 此位。<br>0: 无 PLL2 上锁产生的时钟就绪中断<br>1: PLL2 上锁导致时钟就绪中断        |

| 6   | PLL3RDYFLG | R   | PLL3 就绪中断标志(PLL3 Ready Interrupt Flag)<br>在 PLL3 就绪且 PLL3RDYEN 位被置 1 时,由硬件置 1。<br>由软件通过将 PLL3RDYCLR 位置 1 来清 0 此位。<br>0: 无 PLL3 上锁产生的时钟就绪中断<br>1: PLL3 上锁导致时钟就绪中断        |

| 7   | CSSFLG     | R   | 时钟安全系统中断标志(Clock Security System Interrupt Flag)<br>在外部 3-25MHz 振荡器时钟出现故障时,由硬件置 1。<br>由软件通过将 CSSCLR 位置 1 来清 0 此位。<br>0: 无 HSECLK 失效产生的安全系统中断<br>1: HSECLK 失效导致了时钟安全系统中断 |

| 8   | LSIRDYEN   | R/W | 使能 LSICLK 就绪中断(LSICLK Ready Interrupt Enable)<br>使能或关闭内部 40kHz RC 振荡器就绪中断。<br>0:禁止<br>1:使能                                                                              |

| 9   | LSERDYEN   | R/W | 使能 LSECLK 就绪中断(LSECLK Ready Interrupt Enable)<br>使能外部 32kHz RC 振荡器就绪中断。<br>0:禁止<br>1:使能                                                                                 |

| 10  | HSIRDYEN   | R/W | HSICLK 就绪中断使能(HSICLK Ready Interrupt Enable)<br>使能内部 8MHz RC 振荡器就绪中断。<br>0:禁止<br>1:使能。                                                                                  |

| 11  | HSERDYEN   | R/W | HSECLK 就绪中断使能(HSECLK Ready Interrupt Enable)<br>使能外部 3-25MHz 振荡器就绪中断。<br>0:禁止<br>1:使能                                                                                   |

| 位/域 | 名称         | R/W | 描述                                                                                              |

|-----|------------|-----|-------------------------------------------------------------------------------------------------|

| 12  | PLL1RDYEN  | R/W | PLL1 就绪中断使能(PLL1 Ready Interrupt Enable)<br>使能 PLL1 就绪中断。<br>0:禁止<br>1:使能                       |

| 13  | PLL2RDYEN  | R/W | PLL2 就绪中断使能(PLL2 Ready Interrupt Enable)<br>使能 PLL2 就绪中断。<br>0:禁止<br>1:使能                       |

| 14  | PLL3RDYEN  | R/W | PLL3 就绪中断使能(PLL3 Ready Interrupt Enable)<br>使能 PLL3 就绪中断。<br>0: 禁止<br>1: 使能                     |

| 15  |            |     | 保留                                                                                              |

| 16  | LSIRDYCLR  | W   | 清除 LSICLK 就绪中断(LSICLK Ready Interrupt Clear)<br>清除 LSICLK 就绪中断标志位 LSIRDYFLG。<br>0: 无作用<br>1: 清除 |

| 17  | LSERDYCLR  | W   | 清除 LSECLK 就绪中断(LSECLK Ready Interrupt Clear)<br>清除 LSECLK 就绪中断标志位 LSERDYFLG。<br>0: 无作用<br>1: 清除 |

| 18  | HSIRDYCLR  | W   | 清除 HSICLK 就绪中断(HSICLK Ready Interrupt Clear)<br>清除 HSICLK 就绪中断标志位 HSIRDYFLG。<br>0: 无作用<br>1: 清除 |

| 19  | HSERDYCLR  | W   | 清除 HSECLK 就绪中断(HSECLK Ready Interrupt Clear)<br>清除 HSECLK 就绪中断标志位 HSERDYFLG。<br>0: 无作用<br>1: 清除 |

| 20  | PLL1RDYCLR | W   | 清除 PLL1 就绪中断(PLL1 Ready Interrupt Clear)<br>清除 PLL1 就绪中断标志位 PLL1RDYFLG。<br>0: 无作用<br>1: 清除      |

| 21  | PLL2RDYCLR | W   | 清除 PLL2 就绪中断(PLL2 Ready Interrupt Clear)<br>清除 PLL2 就绪中断标志位 PLL2RDYFLG。<br>0: 无作用<br>1: 清除      |

| 22  | PLL3RDYCLR | W   | 清除 PLL3 就绪中断(PLL3 Ready Interrupt Clear)<br>清除 PLL3 就绪中断标志位 PLL3RDYFLG。<br>0: 无作用<br>1: 清除      |

| 23  | CSSCLR     | W   | 清除时钟安全系统中断(Clock Security System Interrupt Clear)清除安全系统中断标志位 CSSFLG。  0: 无作用  1: 清除             |

| 位/域   | 名称 | R/W | 描述 |

|-------|----|-----|----|

| 31:24 |    |     | 保留 |

# 4.5.4 APB2 外设复位寄存器(RCM\_APB2RST)

偏移地址: 0x0C

复位值: 0x0000 0000

访问: 以字,半字和字节形式访问, 无等待周期。

所有位都可以由软件置位或清 0。

| 位/域 | <u></u> 名称 | R/W | 件直位以有 U。<br>描述                                       |

|-----|------------|-----|------------------------------------------------------|

| 0   | AFIORST    | R/W | 复位复用功能 IO(Alternate Function I/O Reset) 0: 无作用 1: 复位 |

| 1   |            |     | 保留                                                   |

| 2   | PARST      | R/W | 复位 IO 端口 A(IO Port A Reset)<br>0: 无作用<br>1: 复位       |

| 3   | PBRST      | R/W | 复位 IO 端口 B(IO Port B Reset)<br>0: 无作用<br>1: 复位       |

| 4   | PCRST      | R/W | 复位 IO 端口 C(IO Port C Reset) 0: 无作用 1: 复位             |

| 5   | PDRST      | R/W | 复位 IO 端口 D(IO Port D Reset)<br>0: 无作用<br>1: 复位       |

| 6   | PERST      | R/W | 复位 IO 端口 E(IO Port E Reset)<br>0: 无作用<br>1: 复位       |

| 8:7 |            |     | 保留                                                   |

| 9   | ADC1RST    | R/W | 复位 ADC1 (ADC1 Reset) 0: 无作用 1: 复位                    |

| 10  | ADC2RST    | R/W | 复位 ADC2(ADC2 Reset)<br>0: 无作用<br>1: 复位               |

| 11  | TMR1RST    | R/W | 复位 TMR1 定时器(TMR1 Timer Reset)<br>0: 无作用<br>1: 复位     |

| 12  | SPI1RST    | R/W | 复位 SPI1(SPI1 Reset)<br>0: 无作用<br>1: 复位               |

| 13  |            |     | 保留                                                   |

| 位/域   | 名称        | R/W | 描述                                     |

|-------|-----------|-----|----------------------------------------|

| 14    | USART1RST | R/W | 复位 USART1 (USART1 Rreset) 0: 无作用 1: 复位 |

| 31:15 |           |     | 保留                                     |

# 4.5.5 APB1 外设复位寄存器(RCM\_APB1RST)

偏移地址: 0x10 复位值: 0x0000 0000

访问: 以字,半字和字节形式访问, 无等待周期

|       |         |       | 子节形式切问,尤等侍周期<br>               |

|-------|---------|-------|--------------------------------|

| 位/域   | 名称      | R/W   | 描述                             |

|       |         |       | 复位定时器 2(Timer 2 Rreset)        |

| 0     | TMR2RST | R/W   | 0: 无作用                         |

|       |         |       | 1: 复位                          |

|       |         |       | 复位定时器 3(Timer 3 Reset)         |

| 1     | TMR3RST | R/W   | 0: 无作用                         |

|       |         |       | 1: 复位                          |

|       |         |       | 复位定时器 4(Timer 4Rreset)         |

| 0     | TMD4DCT | R/W   | 由软件置 1 或清 0                    |

| 2     | TMR4RST | IK/VV | 0: 无作用                         |

|       |         |       | 1: 复位                          |

|       |         |       | 复位定时器 5(Timer5 Reset)          |

| 3     | TMR5RST | R/W   | 0: 无作用                         |

|       |         |       | 1: 复位                          |

|       |         |       | 复位定时器 6(Timer 6 Reset)         |

| 4     | TMR6RST | R/W   | 0: 无作用                         |

|       |         |       | 1: 复位                          |

|       |         |       | 复位定时器 7(Timer 7 Reset)         |

| 5     | TMR7RST | R/W   | 0: 无作用                         |

|       |         |       | 1: 复位                          |

| 10:6  |         |       | 保留                             |

|       |         |       | 复位窗口看门狗(Window Watchdog Reset) |

| 11    | WWDTRST | R/W   | 0: 无作用                         |

|       |         |       | 1: 复位                          |

| 13:12 |         |       | 保留                             |

|       |         |       | 复位 SPI2(SPI2 Reset)            |

| 14    | SPI2RST | R/W   | 0: 无作用                         |

|       |         |       | 1: 复位                          |

|       |         |       | 复位 SPI3(SPI3 Reset)            |

| 15    | SPI3RST | R/W   | 0: 无作用                         |

|       |         |       | 1: 复位                          |

| 16    |         | 1     | 保留                             |

|       |         |       | ** * *                         |

| 位/域   | 名称        | R/W | 描述                                          |  |  |

|-------|-----------|-----|---------------------------------------------|--|--|

| 17    | USART2RST | R/W | 复位 USART2 (USART2 Reset) 0: 无作用 1: 复位       |  |  |

| 18    | USART3RST | R/W | 复位 USART3 (USART3 Reset) 0: 无作用 1: 复位       |  |  |

| 19    | UART4RST  | R/W | 复位 UART4(UART4 Reset)<br>0: 无作用<br>1: 复位    |  |  |

| 20    | UART5RST  | R/W | 复位 UART5 (UART5 Reset) 0: 无作用 1: 复位         |  |  |

| 21    | I2C1RST   | R/W | 复位 I2C1(I2C1 Reset) 0: 无作用 1: 复位            |  |  |

| 22    | I2C2RST   | R/W | 复位 I2C2(I2C2 Reset) 0: 无作用 1: 复位            |  |  |

| 24:23 | 保留        |     |                                             |  |  |

| 25    | CAN1RST   | R/W | 复位 CAN1 (CAN1 Reset) 0: 无作用 1: 复位           |  |  |

| 26    | CAN2RST   | R/W | 复位 CAN2 (CAN2 Reset) 0: 无作用 1: 复位           |  |  |

| 27    | BAKPRST   | R/W | 复位备份接口(Backup Interface Reset) 0: 无作用 1: 复位 |  |  |

| 28    | PMURST    | R/W | 复位电源接口(Power Interface Reset) 0: 无作用 1: 复位  |  |  |

| 29    | DACRST    | R/W | 复位 DAC (DAC Reset) 0: 无作用 1: 复位             |  |  |

| 31:30 | 保留        |     |                                             |  |  |

## 4.5.6 AHB 外设时钟使能寄存器(RCM\_AHBCLKEN)

偏移地址: 0x14

复位值: 0x0000 0014

访问: 以字,半字和字节形式访问, 无等待周期

所有位都可以由软件置位或清 0。

注:当外设时钟没有启用时,软件不能读出外设寄存器的数值,返回的数值始终 是 0x0。

| 位/域   | <b>名称</b> | R/W | 描述                                                                            |  |

|-------|-----------|-----|-------------------------------------------------------------------------------|--|

| 0     | DMA1EN    | R/W | 使能 DMA1 时钟(DMA1 Clock Enable)<br>0: 关闭<br>1: 开启                               |  |

| 1     | DMA2EN    | R/W | 使能 DMA2 时钟(DMA2 Clock Enable)<br>0: 关闭<br>1: 开启                               |  |

| 2     | SRAMEN    | R/W | 使能 SRAM 时钟(SRAM Interface Clock Enable)<br>使能睡眠模式时 SRAM 时钟。<br>0: 关闭<br>1: 开启 |  |

| 3     |           | •   | 保留                                                                            |  |

| 4     | FMCEN     | R/W | 使能闪存接口电路时钟(FMC Clock Enable)<br>使能睡眠模式时闪存接口电路时钟。<br>0: 关闭<br>1: 开启            |  |

| 5     | 保留        |     |                                                                               |  |

| 6     | CRCEN     | R/W | 使能 CRC 时钟(CRC Clock Enable)<br>0:禁止<br>1:使能                                   |  |

| 11:7  |           |     | 保留                                                                            |  |

| 12    | OTGFSEN   | R/W | 使能 OTG_FS 时钟(OTG_FS Clock Enable)<br>0:禁止<br>1:使能                             |  |

| 13    |           | •   | 保留                                                                            |  |

| 14    | MACEN     | R/W | 使能 Ethernet MAC 时钟(Ethernet MAC Clock Enable)<br>0:禁止<br>1:使能                 |  |

| 15    | MACTXEN   | R/W | 使能 Ethernet MAC TX 时钟(Ethernet MAC TX Clock Enable)<br>0: 禁止<br>1: 使能         |  |

| 16    | MACRXEN   | R/W | 使能 Ethernet MAC RX 时钟(Ethernet MAC RX Clock Enable)<br>0: 禁止<br>1: 使能         |  |

| 31:17 |           |     | 保留                                                                            |  |

# 4.5.7 APB2 外设时钟使能寄存器(RCM\_APB2CLKEN)

偏移地址: 0x18

复位值: 0x0000 0000

访问: 以字, 半字和字节形式访问

通常无访问等待周期。但在 APB2 总线上的外设被访问时,将插入等待状态直到

APB2 的外设访问结束。

所有位都可以通过软件置位或清 0。

注: 当外设时钟没有启用时,软件不能读出外设寄存器的数值,返回的数值始终 是 0x0。

| 位/域   | 名称       | R/W | 描述                                                                |  |  |  |

|-------|----------|-----|-------------------------------------------------------------------|--|--|--|

| 0     | AFIOEN   | R/W | 使能复用功能 IO 时钟(Alternate Function I/O Clock Enable)<br>0:禁止<br>1:使能 |  |  |  |

| 1     |          |     | 保留                                                                |  |  |  |

| 2     | PAEN     | R/W | 使能 IO 端口 A 时钟(I/O Port A Clock Enable)<br>0:禁止<br>1:使能            |  |  |  |

| 3     | PBEN     | R/W | 使能 IO 端口 B 时钟(I/O Port B Clock Enable)<br>0:禁止<br>1:使能            |  |  |  |

| 4     | PCEN     | R/W | 使能 IO 端口 C 时钟(I/O Port C Clock Enable)<br>0:禁止<br>1:使能            |  |  |  |

| 5     | PDEN     | R/W | 使能 IO 端口 D 时钟(I/O Port D Clock Enable)<br>0:禁止<br>1:使能            |  |  |  |

| 6     | PEEN     | R/W | 使能 IO 端口 E 时钟(I/O Port E Clock Enable)<br>0:禁止<br>1:使能            |  |  |  |

| 8:7   | 保留       |     |                                                                   |  |  |  |

| 9     | ADC1EN   | R/W | 使能 ADC1 接口时钟(ADC 1 Interface Clock Enable)<br>0:禁止<br>1:使能        |  |  |  |

| 10    | ADC2EN   | R/W | 使能 ADC2 接口时钟(ADC 2 Interface Clock Enable) 0: 禁止 1: 使能            |  |  |  |

| 11    | TMR1EN   | R/W | 使能 TMR1 定时器时钟(TMR1 Timer Clock Enable) 0: 禁止 1: 使能                |  |  |  |

| 12    | SPI1EN   | R/W | 使能 SPI1 时钟(SPI 1 Clock Enable)<br>0: 禁止<br>1: 使能                  |  |  |  |

| 13    |          | 保留  |                                                                   |  |  |  |

| 14    | USART1EN | R/W | 使能 USART1 时钟(USART1 Clock Enable)<br>0:禁止<br>1:使能                 |  |  |  |

| 31:15 |          |     | 保留                                                                |  |  |  |

## 4.5.8 APB1 外设时钟使能寄存器(RCM\_APB1CLKEN)

偏移地址: 0x1C 复位值: 0x0000 0000

访问: 以字、半字和字节形式访问

通常无访问等待周期。但在 APB1 总线上的外设被访问时,将插入等待状态直到 APB1 外设访问结束。

所有位都可以通过软件置位或清 0。

注: 当外设时钟没有启用时,软件不能读出外设寄存器的数值,返回的数值始终是 0x0。

|       | 定 UXU。   |     | , n. s                                  |  |

|-------|----------|-----|-----------------------------------------|--|

| 位/域   | 名称       | R/W | 描述                                      |  |

|       |          |     | 使能定时器 2 时钟(Timer 2 Clock Enable)        |  |

| 0     | TMR2EN   | R/W | 0: 禁止                                   |  |

|       |          |     | 1: 使能                                   |  |

|       |          |     | 使能定时器 3 时钟(Timer 3 Clock Enable)        |  |

| 1     | TMR3EN   | R/W | 0: 禁止                                   |  |

|       |          |     | 1: 使能                                   |  |

|       |          |     | 使能定时器 4 时钟(Timer 4 Clock Enable)        |  |

| 2     | TMR4EN   | R/W | 0: 禁止                                   |  |

|       |          |     | 1: 使能                                   |  |

|       |          |     | 使能定时器 5 时钟(Timer 5 Clock Enable)        |  |

| 3     | TMR5EN   | R/W | 0: 禁止                                   |  |

|       |          |     | 1: 使能                                   |  |

|       |          |     | 使能定时器 6 时钟(Timer 6 Clock Enable)        |  |

| 4     | TMR6EN   | R/W | 0: 禁止                                   |  |

|       |          |     | 1: 使能                                   |  |

|       |          |     | 使能定时器 7 时钟(Timer74 Clock Enable)        |  |

| 5     | TMR7EN   | R/W | 0: 禁止                                   |  |

|       |          |     | 1: 使能                                   |  |

| 10:6  |          |     | 保留                                      |  |

|       |          |     | 使能窗口看门狗时钟(Window Watchdog Clock Enable) |  |

| 11    | WWDTEN   | R/W | 0: 禁止                                   |  |

|       |          |     | 1: 使能                                   |  |

| 13:12 | 保留       |     |                                         |  |

|       |          |     | 使能 SPI2 时钟(SPI 2 Clock Enable)          |  |

| 14    | SPI2EN   | R/W | 0: 禁止                                   |  |

|       |          |     | 1: 使能                                   |  |

|       |          |     | 使能 SPI3 时钟(SPI 3 Clock Enable)          |  |

| 15    | SPI3EN   | R/W | 0: 禁止                                   |  |

|       |          |     | 1: 使能                                   |  |

| 16    |          |     | 保留                                      |  |

|       |          |     | 使能 USART2 时钟(USART 2 Clock Enable)      |  |

| 17    | USART2EN | R/W | 0: 禁止                                   |  |

|       |          |     | 1: 使能                                   |  |

|       |          |     | 使能 USART3 时钟(USART 3 Clock Enable)      |  |

| 18    | USART3EN | R/W | 0: 禁止                                   |  |

|       |          |     | 1: 使能                                   |  |

| L     | l        |     | L                                       |  |

| 位/域   | 名称      | R/W | 描述                                                        |  |

|-------|---------|-----|-----------------------------------------------------------|--|

| 19    | UART4EN | R/W | 使能 UART4 时钟(UART 4 Clock Enable)<br>0:禁止<br>1:使能          |  |

| 20    | UART5EN | R/W | 使能 UART 5 时钟(UART 5 Clock Enable)<br>0:禁止<br>1:使能         |  |

| 21    | I2C1EN  | R/W | 使能 I2C1/3 时钟(I2C1/3 Clock Enable) 0: 禁止 1: 使能             |  |

| 22    | I2C2EN  | R/W | 使能 I2C2/4 时钟(I2C2/4 Clock Enable)<br>0:禁止<br>1:使能         |  |

| 24:23 | 保留      |     |                                                           |  |

| 25    | CAN1EN  | R/W | 使能 CAN1 时钟(CAN1 Clock Enable)<br>0:禁止<br>1:使能             |  |

| 26    | CAN2EN  | R/W | 使能 CAN2 时钟(CAN2 Clock Enable)<br>0:禁止<br>1:使能             |  |

| 27    | BAKPEN  | R/W | 使能备份接口时钟(Backup Interface Clock Enable)<br>0:禁止<br>1:使能   |  |

| 28    | PMUEN   | R/W | 使能电源接口时钟(Power Interface Clock Enable) 0: 禁止 1: 使能        |  |

| 29    | DACEN   | R/W | 使能 DAC 接口时钟(DAC Interface Clock Enable)<br>0: 禁止<br>1: 使能 |  |

| 31:30 |         |     | 保留                                                        |  |

### 4.5.9 备份域控制寄存器(RCM\_BDCTRL)

偏移地址: 0x20

复位值: 0x0000 0000, 只能由备份域复位有效复位访问: 以字、半字和字节形式访问, 0 到 3 等待周期当连续对该寄存器进行访问时,将插入等待状态。

注意: 当 PMU\_CTRL 中的 BPWEN 位被置 1 后, LSEEN、LSEBCFG、

RTCSRCSEL 和 RTCCLKEN 才能进行改动。

| 位/域 | 名称        | R/W | 描述                                                               |

|-----|-----------|-----|------------------------------------------------------------------|

| 0   | LSEEN     | R/W | 使能 LSECLK(Low-Speed External Clock Enable)<br>0:禁止<br>1:使能       |

| 1   | LSERDYFLG | R   | LSECLK 就绪标志(Low-Speed External Oscillator Oscillator Ready Flag) |

| 位/域   | 名称        | R/W  | 描述                                                                          |

|-------|-----------|------|-----------------------------------------------------------------------------|

|       |           |      | LSECLK 稳定时硬件置 1,不稳定时硬件清 0。LSEEN 被清零后,需要 6 个外部低速振荡器的周期才会清除此位。                |

|       |           |      | 0: 未就绪                                                                      |

|       |           |      | 1: 就绪                                                                       |

|       |           |      | 配置 LSECLK 为旁路模式(Low-Speed External Clock Bypass Mode Configure)             |

| 2     | LSEBCFG   | R/W  | 旁路模式指外部时钟作为 LSECLK 时钟源,否则谐振器作为 LSECLK 时钟源。                                  |

|       |           |      | 0: 非旁路模式                                                                    |

|       |           |      | 1: 旁路模式                                                                     |

| 7:3   |           |      | 保留                                                                          |

|       |           |      | 选择 RTC 时钟源(RTC Clock Source Select)<br>先设置 BDRST 位复位备份域,再选择 RTC 时钟源,无法直接配置该 |

|       |           |      | 寄存器修改。                                                                      |

| 9:8   | RTCSRCSEL | R/W  | 00: 无时钟                                                                     |

|       |           |      | 01: LSECLK 振荡器作为 RTC 时钟<br>10: LSICLK 振荡器作为 RTC 时钟                          |

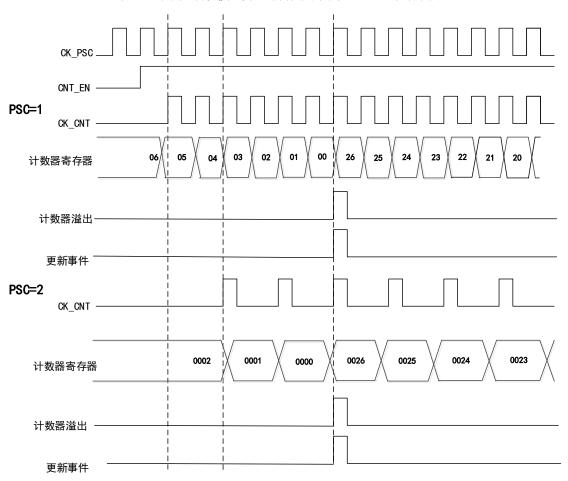

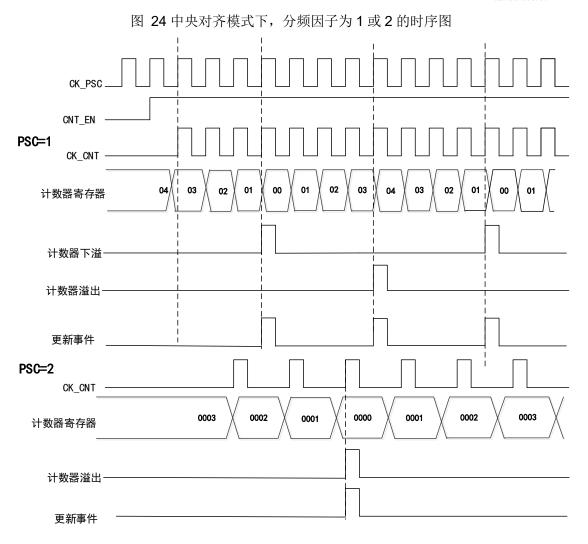

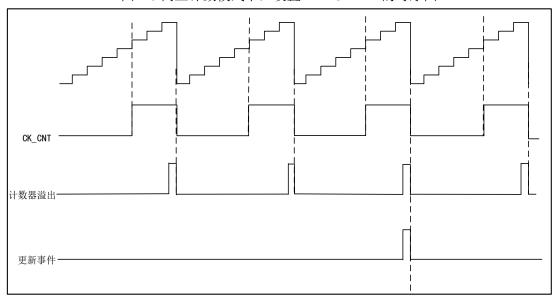

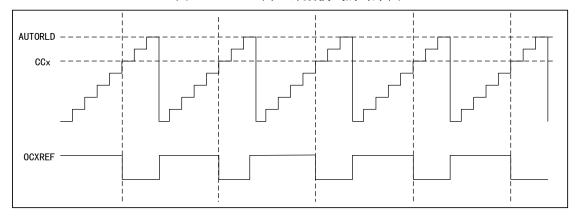

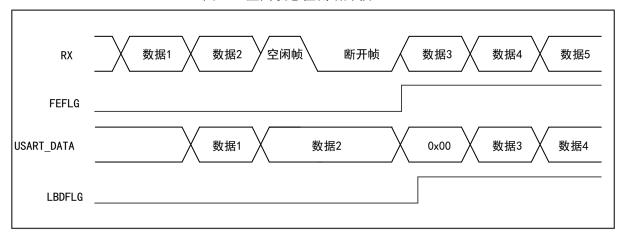

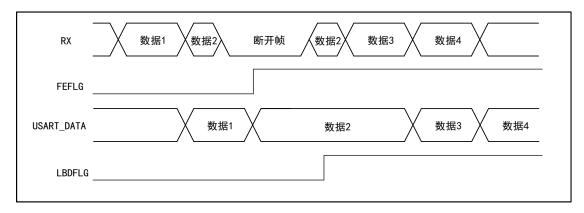

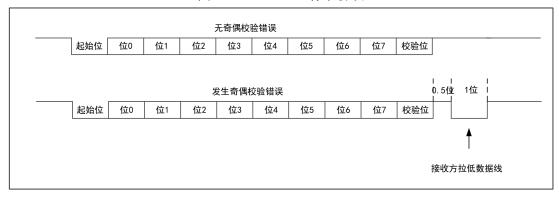

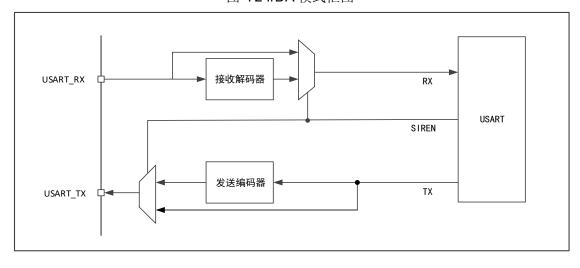

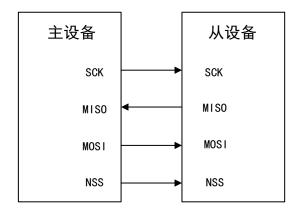

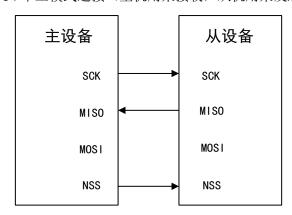

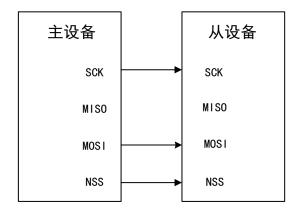

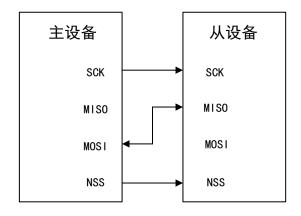

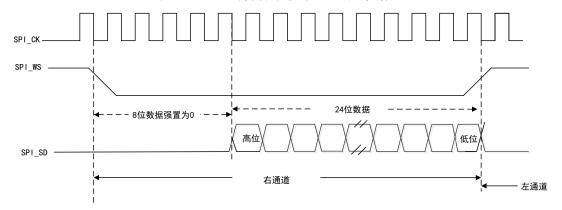

|       |           |      | 11: HSECLK 振荡器在 128 分频后作为 RTC 时钟                                            |